Vitis

Vitis 【Hello World編(1)】Vitisで”Hello World”プログラムを実行してみた – ハードウェア構成 –

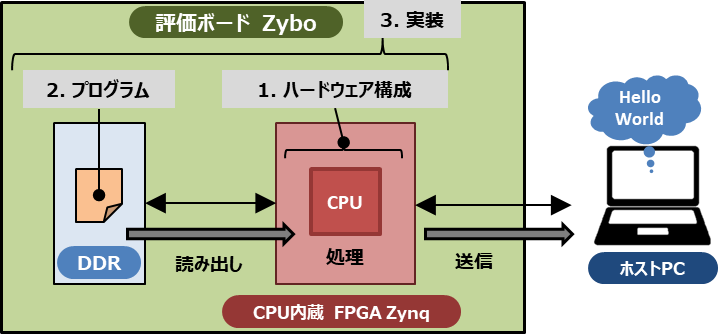

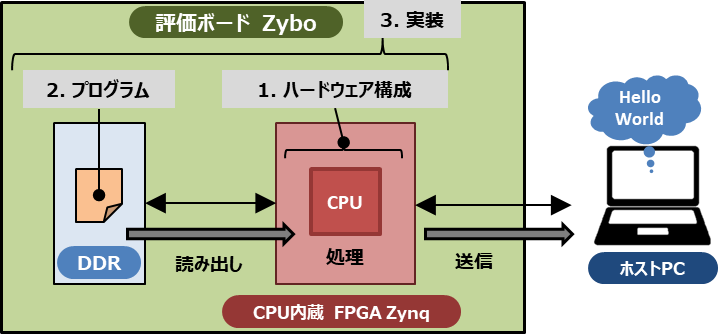

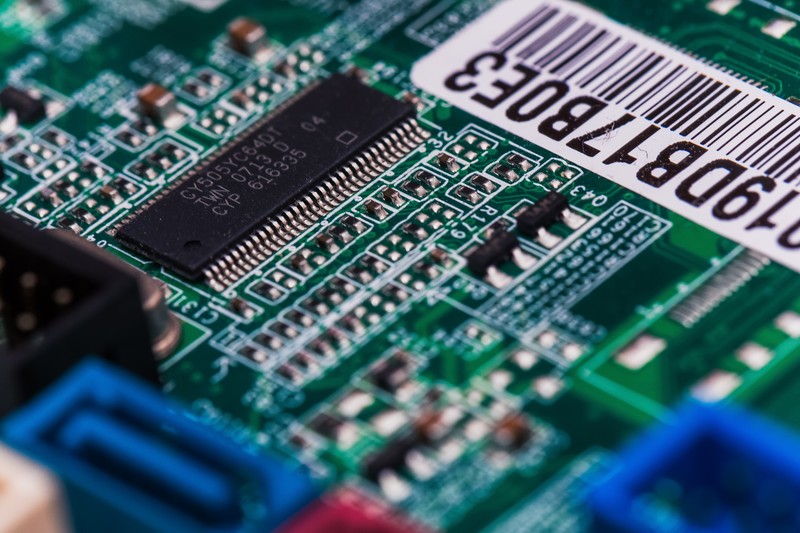

本記事ではVitisとVivadoを用いてZybo上のHelloWorldを出力するアプリケーションの作成をめざします。まず、Zynq CPU上でHelloWorldプログラムを動かすために、Zynqのハードウェア構成を定めるプロジェクトを作成しました。

Vitis

Vitis  Vitis

Vitis  Xilinx SoC

Xilinx SoC  Vitis

Vitis