本記事の概要

- XilinxのIPコア Video Timing Controllerは、ビデオ信号におけるタイミング信号を検出・生成するためのIPコア

- タイミング信号は例えば以下の5種類で、各信号のアクティブ期間を検出・生成する。

| 信号名 | 用途 |

| active_video_in(out) | 表示期間の間のみHigh状態 |

| hblank_in(out) | 水平ブランキング期間の間のみHigh状態 |

| hsync_in(out) | 水平同期期間の間のみHigh状態 |

| vblank_in(out) | 垂直ブランキング期間の間のみHigh状態 |

| vsync_in(out) | 垂直同期期間の間のみHigh状態 |

- 検出したステータス信号と生成するための制御信号は、外部プロセッサからAXI4-Lite経由で参照することが可能

XilinxのIPコア Video Timing Controller(VTC) は、ビデオを出力するときにタイミングを同期するための信号を生成したり、逆に外部から入力されたビデオを解析し、そのビデオのタイミングやフォーマットを検出してくれる、非常に便利なIPです。

過去の記事では、「Vitis」でのビジョンライブラリを試す前準備として、Digilent社が提供するHDMI出力デモのサンプルプログラムを読み込みました。その際にも、ビデオのタイミング生成にVideo Timing Controllerが使用されています。

本IPは便利である一方で、使える機能が多様な分、実際に使う上でリファレンスマニュアルを読み込むのに苦労しました。

そこで、本記事ではまず最初に使うにあたって、最低限知っておくと良い項目について、筆者なりにまとめてみました。

- FPGAの開発に興味のある学生

- Vitisを用いたアプリケーション開発は未経験のエンジニア

- FPGAでの動画像処理を行いたいエンジニア

それでは、興味のある方はぜひ最後までご覧ください!

Video Timing Controllerの機能

概要

ビデオ信号の画像処理や画像認識の高速化に、FPGAの活用を検討しようとしている事例が増えています。例えば、カメラで取得した画像から、FPGA上で高速にノイズの多い画像から特定の領域を強調したり、人物や物体を認識させたりといった用途ですね。

また、画像処理を施した生成画像をFPGAから外部のディスプレイに送信することもあると思います。

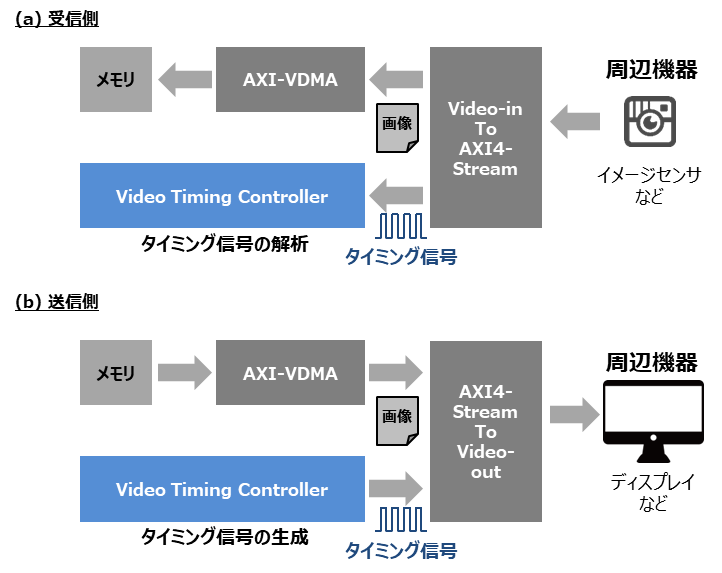

一般に、ビデオ信号は画像信号とそれを適切なタイミングに同期して送信するタイミング信号とを組み合わせて構成されます。画像処理をビデオ信号に対して行うには、FPGA上で一旦、ビデオ信号を画像信号とタイミング信号とに分割して考えます。画像信号に対してのみ、所定の画像処理を行います。そして、最終的に外部に出力する際に、受信したタイミング信号と同じフォーマットになるように、改めてタイミング信号を生成して、画像信号と合わせてビデオ信号を生成します。

Xilinx社提供のIPコアVideo Timing Controllerは、

・分割したタイミング信号がどういったフォーマットなのかを検出

・ビデオ信号を送信する際に所望のフォーマットになるようにタイミング信号を生成

という2つの機能を有するIPコアとなっています。

- ビデオ信号におけるタイミング信号の検出

- ビデオ信号におけるタイミング信号の生成

Video Timing Controllerには制御レジスタが用意されており、そこに書き込まれた設定値に従ってタイミング信号が生成されます。

この制御レジスタはVivadoのGUI上で固定値として設定することが可能です。例えば、すでに入力してある動画像を特定の決まったフォーマットで外部に送信する場合には、決め打ちでこの固定値を指定してしまえば良いでしょう。

また、オプションでAXI4-Liteのインターフェースを設けることも可能です。このとき、プロセッサユニットから制御信号をAXI4-Lite経由で送信し、設定パラメータを動的に制御します。また、Video Timing Controllerで検出したタイミング信号のフォーマットを読み出すことも可能です。

- 制御パラメータの変更が不要であれば、VivadoのGUI上で固定値で設定。

- ドライバを活用してプロセッサ(MicroblazeやZynqのARMコアなど)からAXI4-Lite経由で制御レジスタを変更し、動的に設定パラメータを変更したり、検出したタイミング信号のフォーマットを読み出すことも可能。

ビデオ信号にタイミングの概念は必須ですからね。

次に、どういったタイミング信号を用いて、外部のディスプレイにビデオを送信しているのかを確認しておきましょう。

※注意:Video Timing Controllerで扱える最大解像度は2021年3月現在8192×8192(ブランキング期間含む)までです。ここまで大きい解像度の画像を扱うことはほとんどないと思いますが、ご注意ください。

タイミング信号のフォーマット

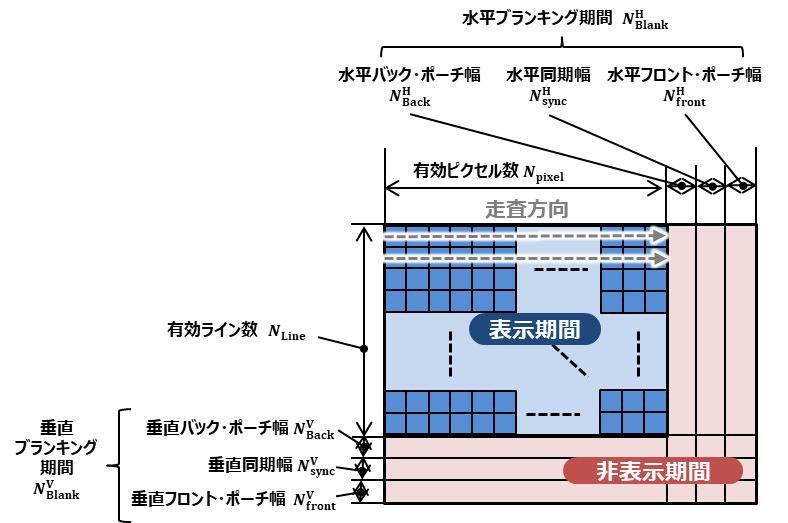

ブランキング期間

ディスプレイへの表示では、各画素(ピクセル)ごとに順番に画像を描画していきます。このとき左端から1画素ごとに水平方向に描画し(水平走査)、1ラインの描画が完了したら、また左端に戻り次の1ラインの描画を開始します。そして、水平走査を一番下側のラインに達するまで垂直方向に順次描画していきます(垂直走査)。

かつてディスプレイ機器の代表であったブラウン管のテレビでは、電子ビームを左から右に走査した走査線が、画像を描画していました。ブラウン管では、1ラインの描画が完了し電子ビームを左側や上側に戻す帰線の処理を行うときに、描画ができない期間が発生します。そこで、水平ブランキング期間と垂直ブランキング期間と呼ばれる、描画を行わない非表示期間が設けられています。

また、ディスプレイに画像を表示するとき、送受信側で走査のタイミングを同期させる必要があります。そこで、ブランキング期間の間に走査のタイミングを決めるための同期信号を送る期間を設けています。これが同期期間になります。

タイミング信号の構成

タイミング信号は、基本的には検出と生成のいずれにおいても、次の表に示す5種類を抑えておくと良いと思います(※)。以下では、この5種類の信号がどのようなタイミングで出力されるかを確認します。

※オプション設定次第では、別の信号(field_id_inやactive_chroma_in)を追加したり、削除したりすることも可能ですが、まずはこの基本の5つを抑えておくと良いと思います。

| 信号名 | 用途 |

| active_video_in(out) | 表示期間の間のみHigh状態 |

| hblank_in(out) | 水平ブランキング期間の間のみHigh状態 |

| hsync_in(out) | 水平同期期間の間のみHigh状態 |

| vblank_in(out) | 垂直ブランキング期間の間のみHigh状態 |

| vsync_in(out) | 垂直同期期間の間のみHigh状態 |

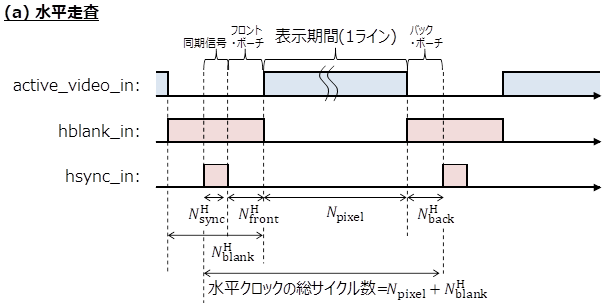

水平同期信号

まず、水平走査におけるブランキング期間のタイミングチャートについて詳しく見ていきましょう。画像の1ラインでの各信号のタイミングチャートは図のとおりです。

水平同期信号hsync_inが生成した後、表示期間の前にフロント・ポーチと呼ばれる非表示期間を設けています。その後、1ライン分の描画を行った後、バック・ポーチと呼ばれる非表示期間を設けています。これが水平方向1ライン分の走査になります。この水平走査を全ラインの分だけ繰り返して、1フレームの描画を実行します。

表示期間の間にactive_video_inがHigh状態になり、水平ブランキング期間の間にhblank_inがHigh状態、同期期間の間にhsync_inがHigh状態に立ち上がります。

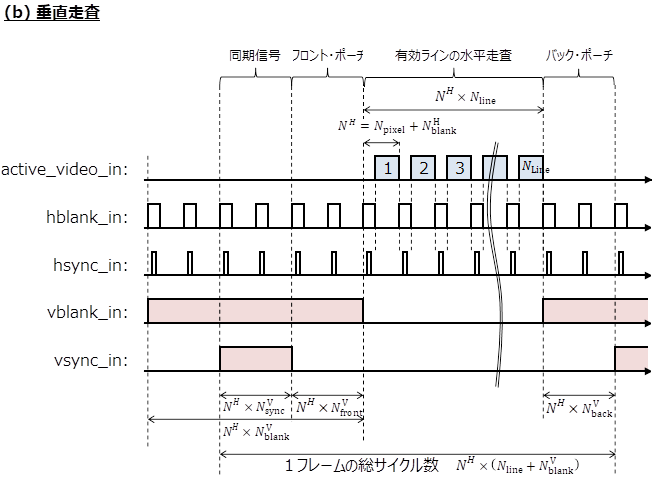

垂直同期信号

次に、垂直同期信号について見ていきましょう。画像全体での各信号のタイミングチャートは図のとおりです。

垂直同期信号が生成された後、垂直フロント・ポーチが続きます。垂直フロント・ポーチが完了すると、表示期間が始まります。有効ライン数だけの水平走査が完了すると、次に垂直バック・ポーチが続きます。

垂直バック・ポーチ、垂直同期信号、垂直フロント・ポーチを合わせた期間が、垂直ブランキング期間となり、非表示期間が続きます。この非表示期間の間は、vblank_inがHigh状態に立ち上がります。

1ラインの走査に必要なクロック数と、1フレーム全体の走査に必要なクロック数についてまとめると次の通りです:

- 1ラインの走査に必要なクロック数:有効ピクセル数\( N_\mathrm{pixel} +\)水平ブランキング期間のピクセル数\( N^\mathrm{H}_\mathrm{blank} \)

- 1フレームの走査に必要なライン数:有効ライン数\( N_\mathrm{line} +\)垂直ブランキング期間のライン数\( N^\mathrm{V}_\mathrm{blank} \)

- 1フレームの走査に必要なクロック数:\( (N_\mathrm{pixel} +N^\mathrm{H}_\mathrm{blank}) \times ( N_\mathrm{line} + N^\mathrm{V}_\mathrm{blank}) \)

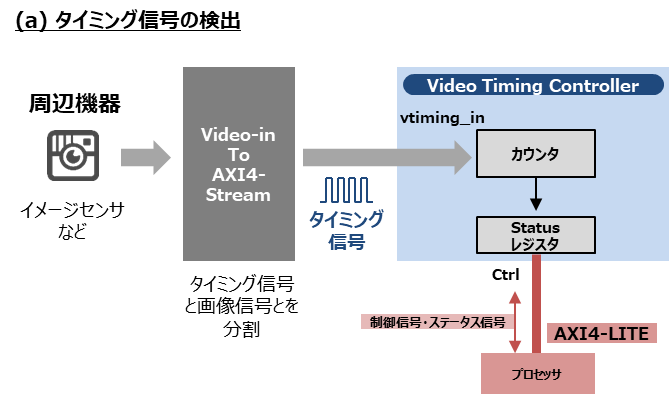

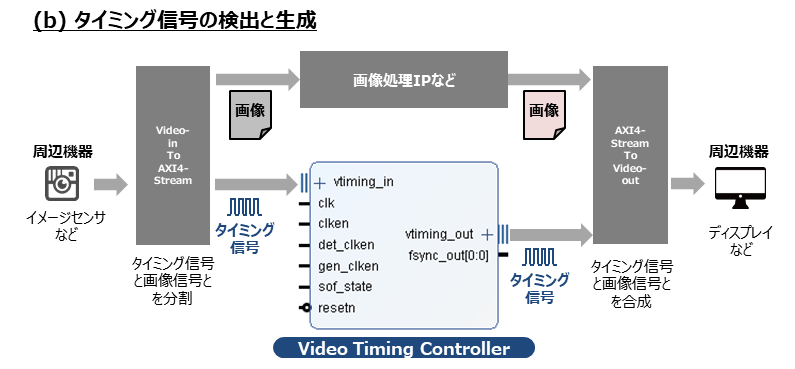

ビデオタイミングの検出

ビデオ信号は”Video-in To AXI4-Stream”というIPコアで画像信号とタイミング信号に分割され、抽出したタイミング信号をVideo Timing Controller IPのvtiming_inというバスに入力することによって、フォーマットを検出することができます。

vtiming_inというバスには、先程の表にまとめた5種のポート(active_video_in, hblank_in, hsync_in, vblank_in, vsync_in)が束ねられています。

タイミング信号は、IPコア内のカウンタを用いて検出されます。検出するのは、例えば、有効ピクセル数 \( N_\mathrm{pixel} \)や水平同期期間におけるピクセル数 \(N^\mathrm{H}_\mathrm{sync} \)などです。カウントした結果は、ステータス・レジスタに格納され、AXI4-Lite経由で外部のプロセッサで読み出すことが可能です。

また、タイミング信号の検出結果は外部に出力せずに、直接ビデオタイミングの生成に用いることも可能です。

検出した信号はそのまま使うこともできますが、少しだけフォーマットを変えた使い方もできます。例えば、検出したイメージセンサのデジタル信号の極性とディスプレイの制御信号の極性が反転している場合、タイミング信号の極性を反転させたりといった使い方も可能です。

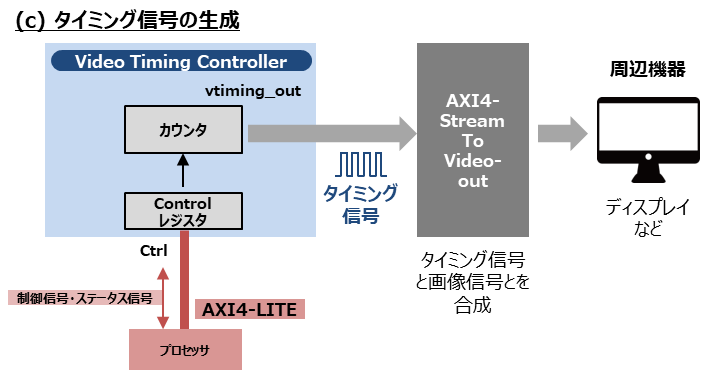

ビデオタイミングの生成

タイミング信号の生成では、Vivadoのブロックダイアグラム上で出力タイミングを決めて、特定のフォーマットで出力します。また、設定値の書き込みは、AXI4-Lite経由で制御レジスタに外部プロセッサから行うこともオプション設定で可能です。

タイミング信号はvtiming_outというバスから出力され、”AXI4-Stream To Video-out”という別のIPコアで画像信号と合成してディスプレイに出力します。

※”AXI4-Stream To Video-out”からのRGB信号をVGA規格やDVI規格(HDMI出力)に変換するためのIPコアはDiligent社から提供されています。

ステータス・レジスタや制御レジスタのアドレスマップについては、リファレンスシートを参照するとよいでしょう。ブロックダイアグラムの設定方法やプロセッサを用いたステータス・レジスタと制御レジスタの参照方法については、長くなりそうなので別記事にまとめていく予定です。

ビデオ入出力系のIPは種類が多く、それぞれの奥が深いので、自在に操れるようになるのが楽しみですね。IPの使い方について継続的に記事にまとめていきますので、今後ともご覧いただければと思います。

ここまで読んでいただき、ありがとうございました。

次回の記事へのリンク

参考資料

https://www.xilinx.com/support/documentation/ip_documentation/v_tc/v6_1/pg016_v_tc.pdf

コメント