本記事の概要

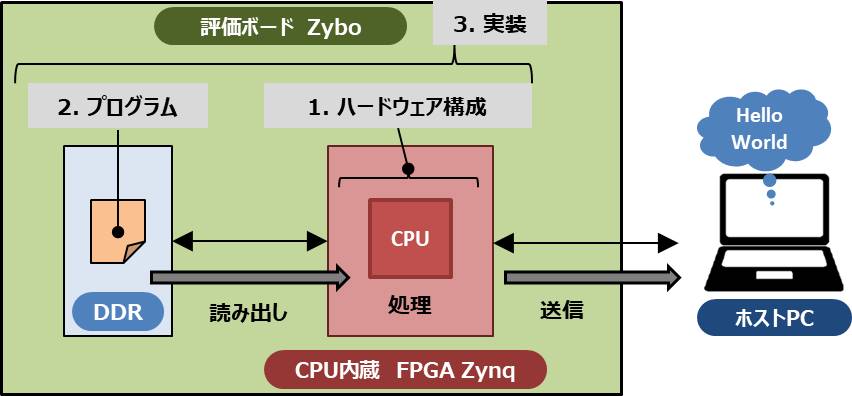

本記事ではVitisとVivadoを用いてZybo上のHelloWorldを出力するアプリケーションの作成をめざします。まず、Zynq CPU上でHelloWorldプログラムを動かすために、Zynqのハードウェア構成を定めるプロジェクトを作成しました。

これまでFPGAを用いたシステム開発には、ハードウェア設計にVivado、ソフトウェアアプリケーションの開発にXilinx SDKを用いられてきました。

しかし、2019年以降、ソフトウェアアプリケーションの開発は、Xilinx SDKから統合ソフトウェア開発環境「Vitis」へと移行しています。

「Vitis」での開発環境に慣れ親しんでおくためにも、Xilinx SDK 2019.1で作成した”Hello World”アプリケーションを、Vitis 2020.2でも作成してみました。

今回の記事では、統合ソフトウェア開発環境Vitis 2020.2とXilinx FPGA向け設計ツール Vivado 2020.2を用いて、開発ボードZybo (搭載SoCチップ Zynq)に実装する”Hello World”アプリケーションを作成する方法についてまとめます。

- FPGAプログラミングの初学者

- FPGAの開発に興味のある学生

- Vitisを用いたアプリケーション開発は未経験のエンジニア

それでは、興味のある方はぜひ最後までご覧ください!

目標と工程

開発目標

本記事の目標は次の通りです:

統合ソフトウェア開発環境VitisとFPGA設計環境Vivadoを用いて

“Hello World”文字列をZynqからホストPCへと送信するアプリケーションを作成する

開発工程

Hello Worldプロジェクトを作成するにあたり、次のリンク先のFPGAプログラミング大全を参考にしています。

ZynqやMicroblazeなどのプロセッサを活用したシステム開発の方法が丁寧に記載されているので、初学者がさらにステップアップするのに非常に素晴らしい書籍だと思います。

システムの構成

開発環境

- 開発用PC: Windows 10, 64bit

- Vivado Design Suite – HLx Edition – 2020.2

- Vitis コア開発キット – 2020.2

- 開発用基板: Zybo Zynq-7010評価ボード(Board Rev.4)

- Zynq XC7Z010-1CLG400C

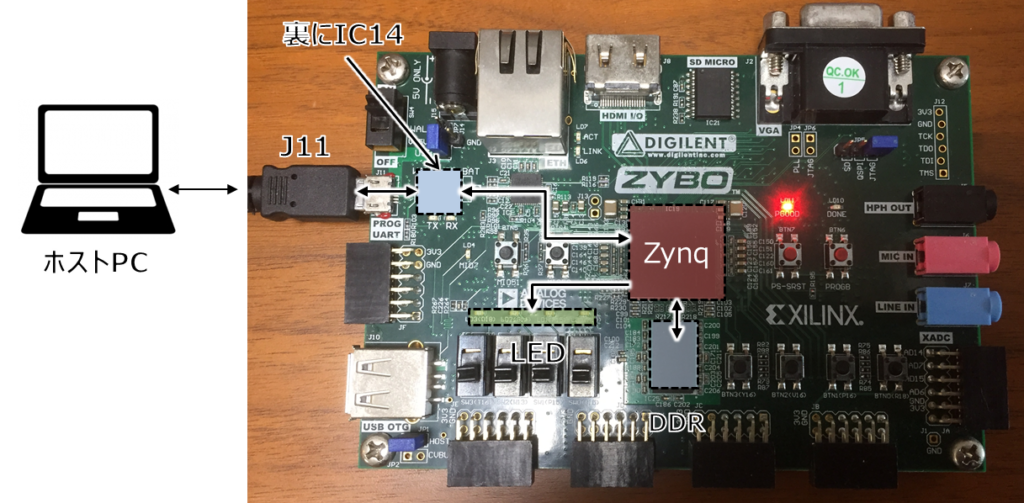

開発ボード Zybo Zynq-7010評価ボード

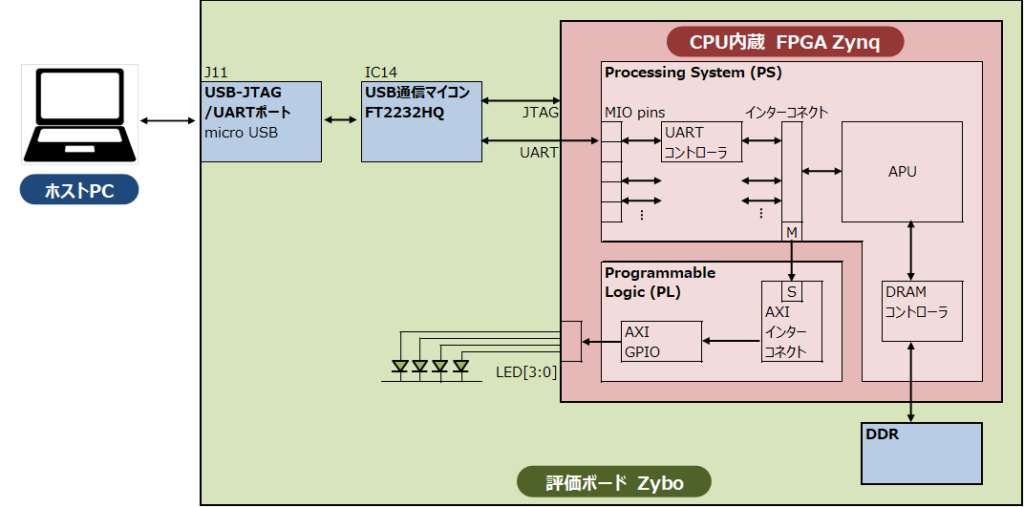

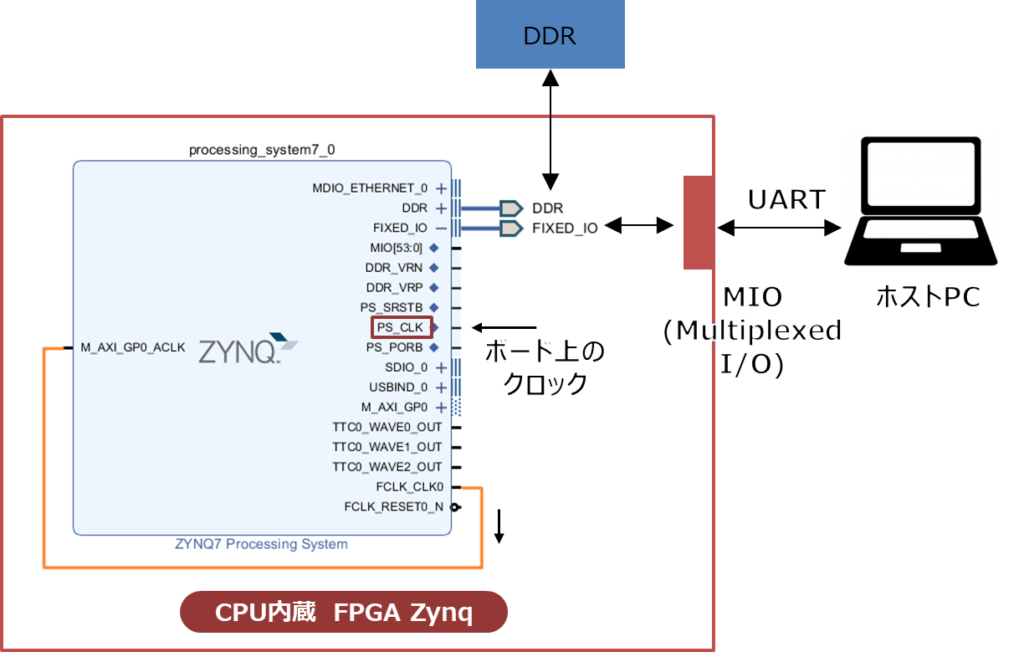

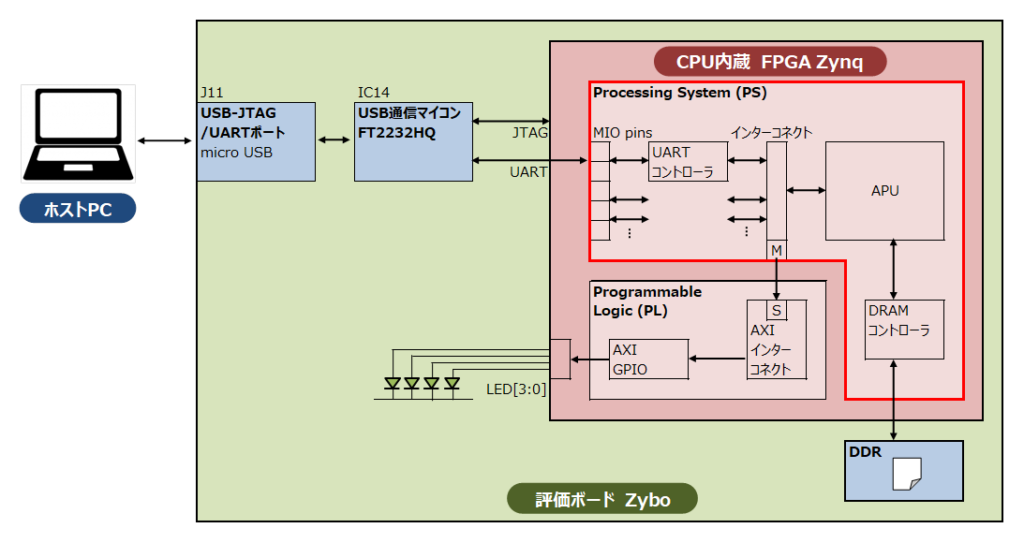

Zyboのシステム構成図

Zyboのマニュアルを参考にまとめると、以下のようなシステム構成になります。

※本記事で必要なところのみを抜粋しています。実際の回路基板には他にも多くの有用な機能が含まれます。

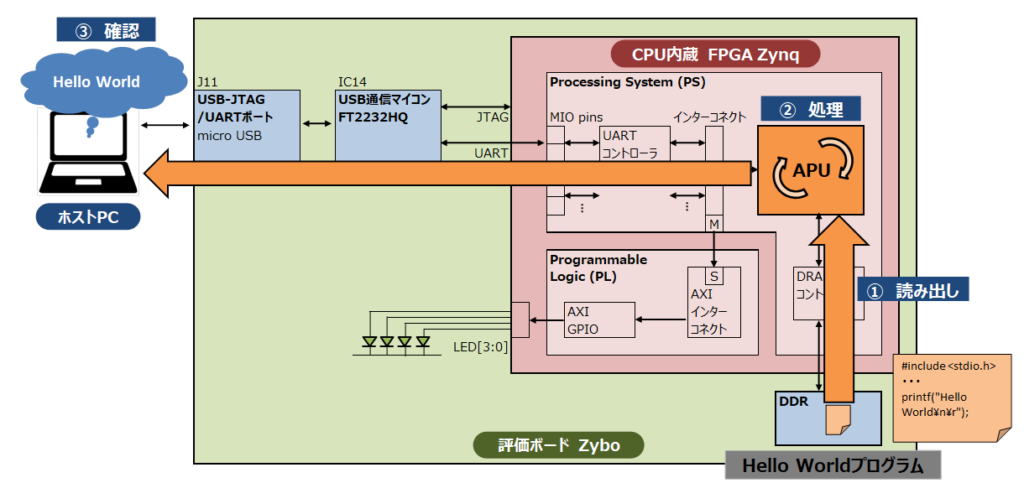

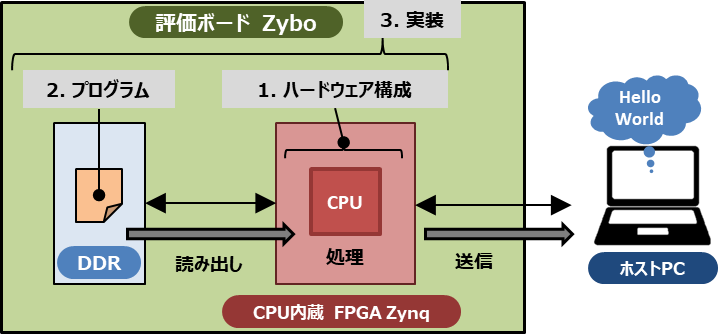

動作原理

動作原理のポイントは以下の通りです。

① DDRメモリから”Hello World”プログラムを読み込む

② CPUで処理

③ 処理結果をホストPCで確認

動作させるために、必要なプロジェクトとプログラムを設計していきます。

Xilinx FPGA向けの開発ツール”Vivado Design Suite”(通称、Vivado)でロジックを設計し、

ホストPCからJTAG経由で、PL (Programmable Logic ;Zynq上で回路を構築するFPGA部分)に設計したロジックを書き込みます。

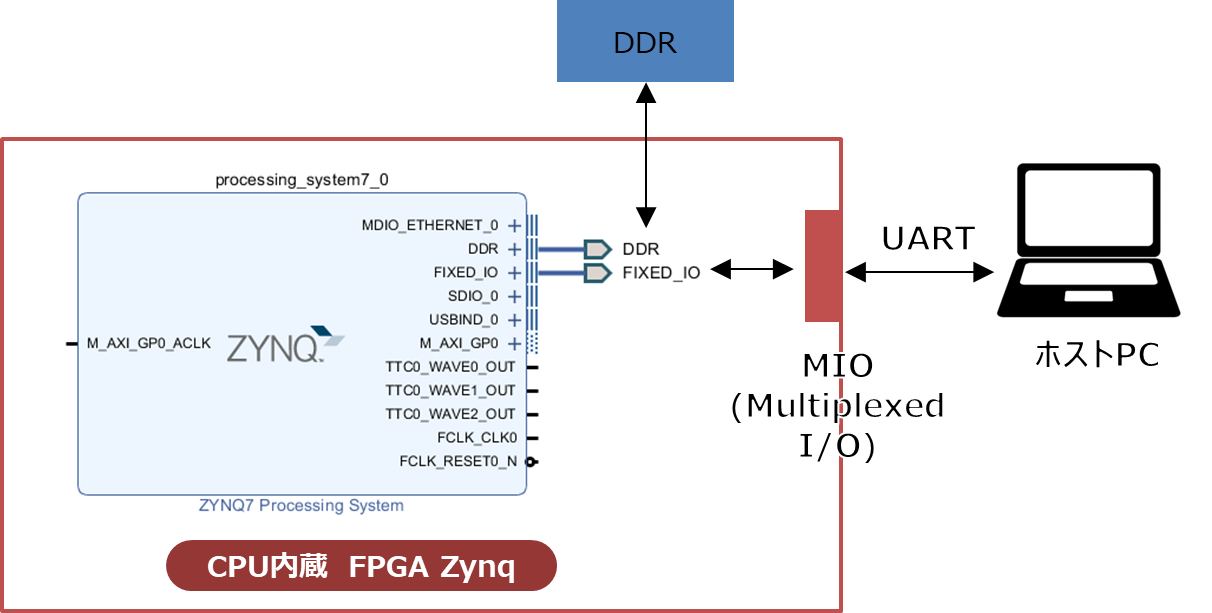

PS(Processing System;CPUに加え、イーサネットやUSB、DDRメモリと通信するための周辺回路も内蔵されたブロック)とホストPCは、シリアルポートのUARTを介して交信します。

”Hello World”の文字列は、UARTを経由してPS内のAPU(Application Processor Unit;デュアルコアのCPU+α)からシリアル通信でホストPCに送信されます。

受信した文字列は、ホストPCで確認しましょう。

DDRメモリには、CPUを動かすためのプログラムが格納されています。

今後、LED点滅も試してみるので、ブロック図にはLED出力端子も記載しましたが、本日のテーマではこのモジュールは必要ありません。

プロジェクトの作成

準備作業(Zyboのボードの読み込み)

新しいプロジェクトを作成する前に、Zyboのボードに関するファイルを読み込んでおく必要があります。

ボードファイルの読み込み方法は、この記事を参照してください。

ハードウェア設計(CPUと周辺回路の構成)

Vivado 2020.2のプロジェクトの作成

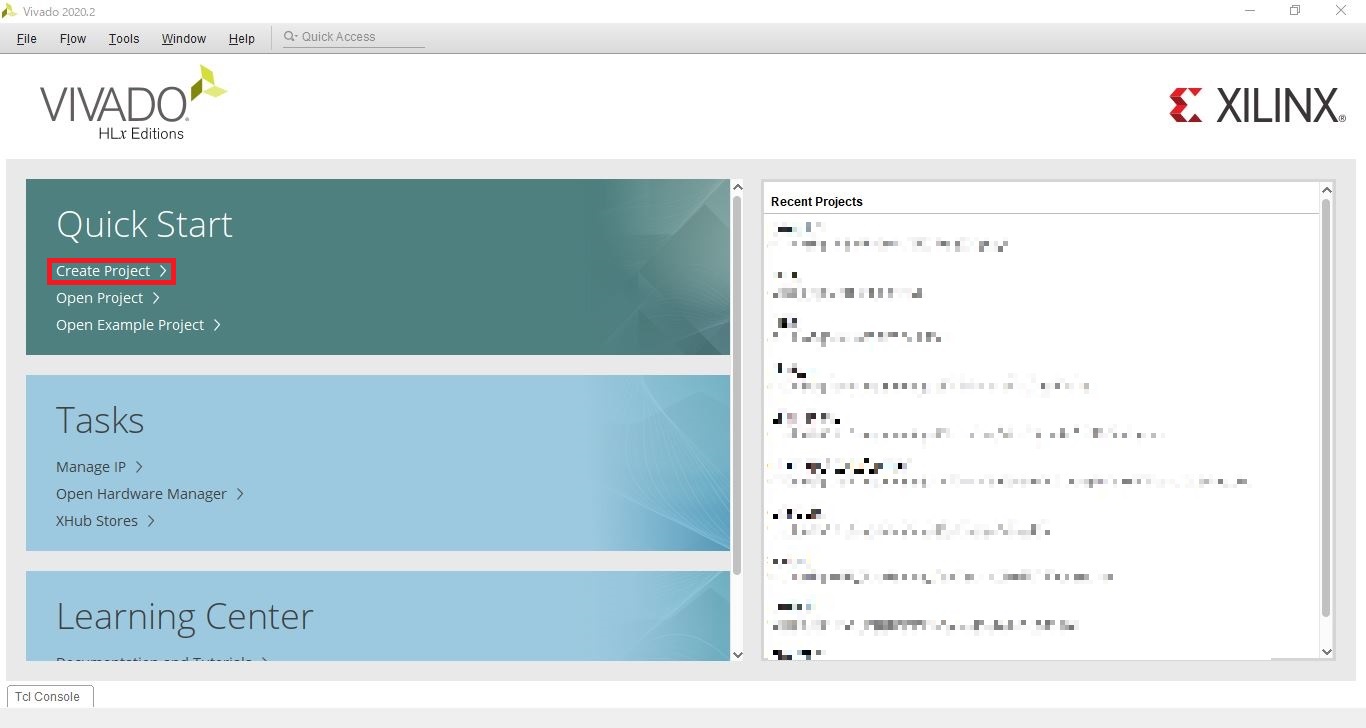

Vivado 2020.2を立ち上げ、[Create Project]をクリックし、新しいプロジェクトを作成します。

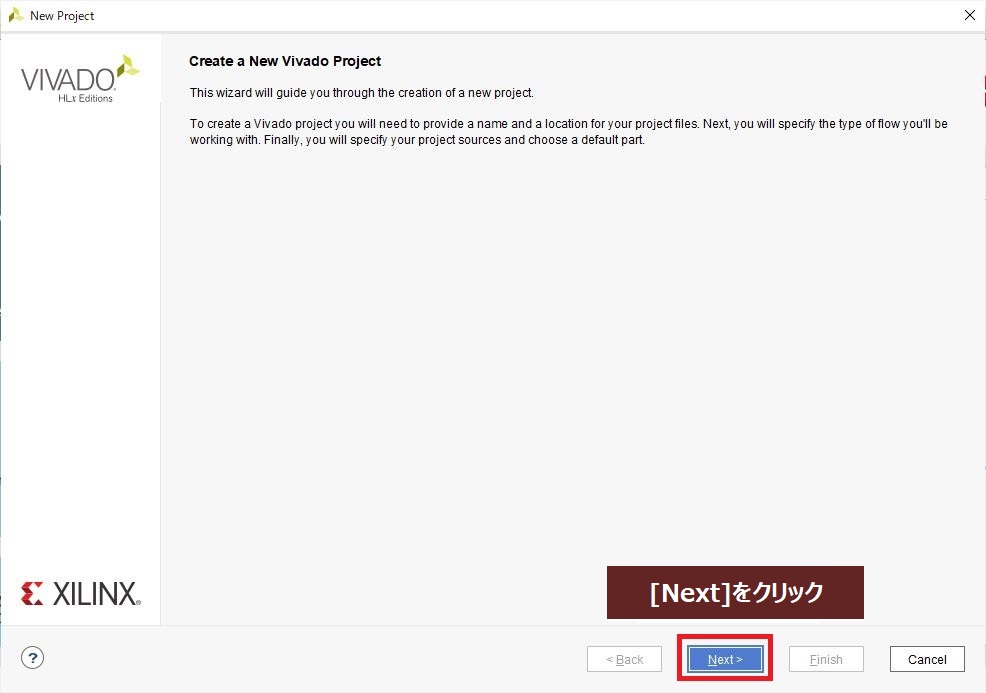

新しいプロジェクトを作成するための、設定を入力するウィンドウが立ち上がります。

設定に必要な情報を順番に入力していきましょう。

最初のウィンドウで[Next]をクリックします。

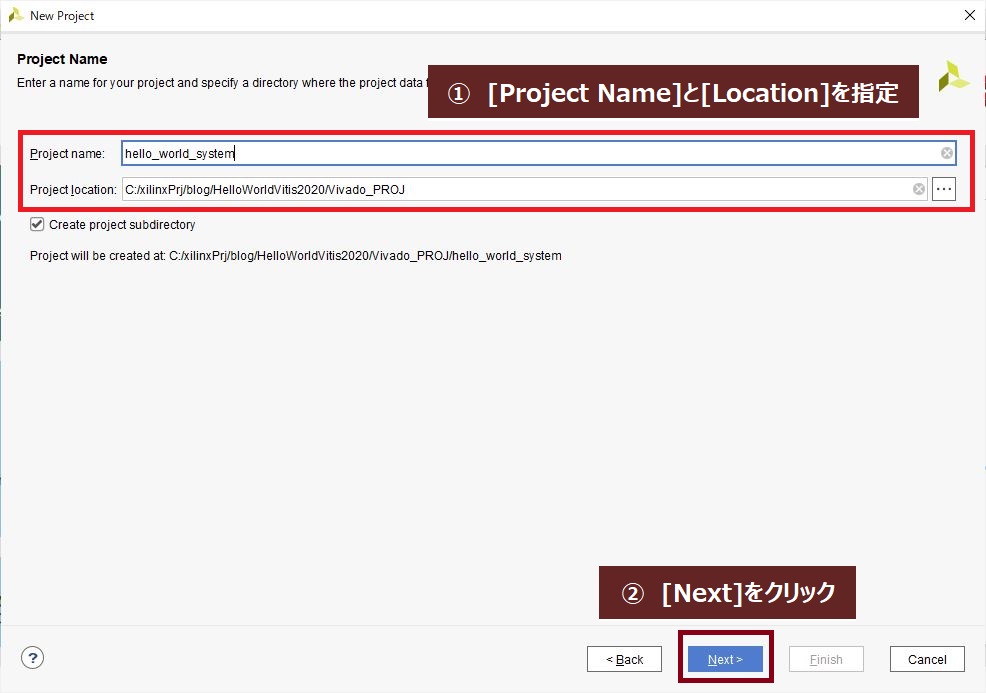

次に、プロジェクト名を設定します。

今回、プロジェクト名を[hello_world_system]とし、プロジェクトを格納するフォルダを指定します。入力が完了したら、[Next]をクリックします。

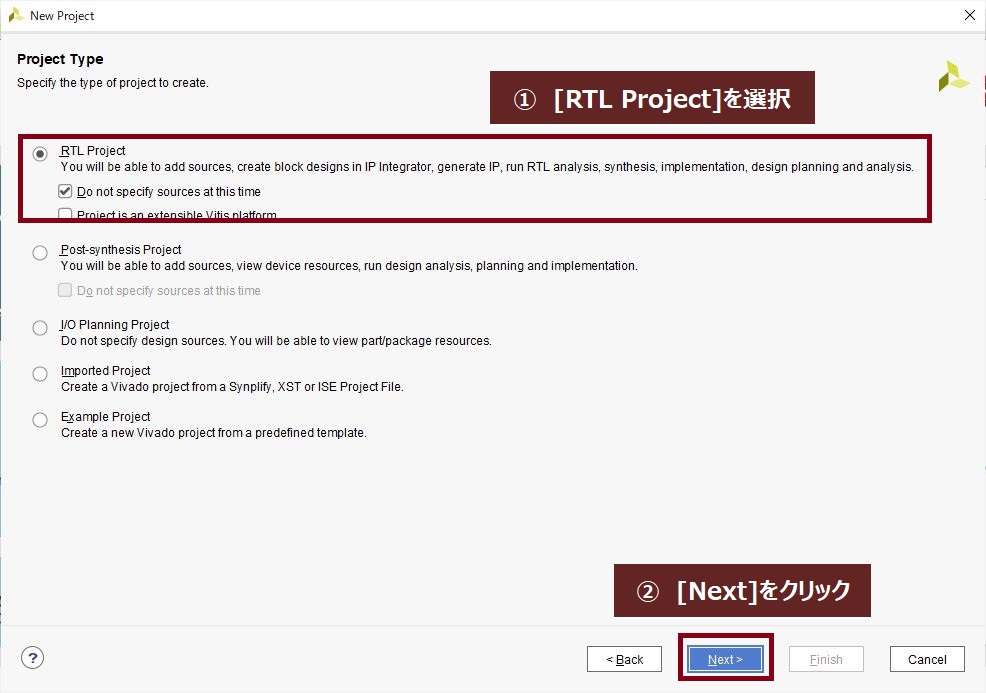

次に、プロジェクトの形式を指定します。ここは、デフォルトの[RTL Project]をそのまま指定しておき、[Next]をクリックします。

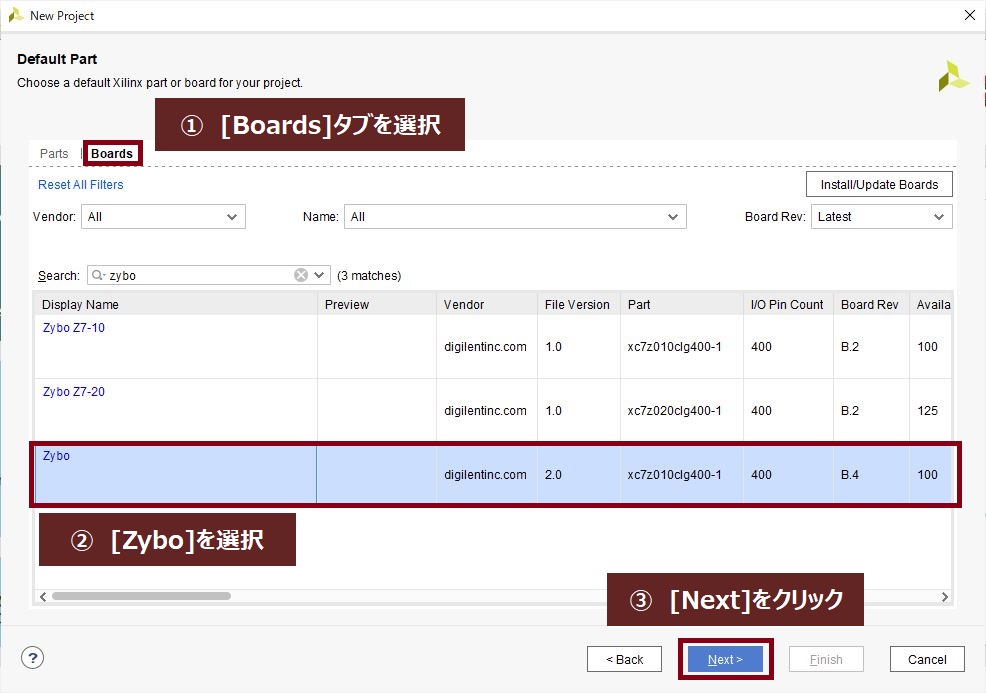

次に、システムを構築する、FPGAチップまたは回路基板の種類を選択します。

ここでは、すでに設定を読み込んでいるZyboのボードを指定します。

まず、[Boards]タブを選択肢、Search欄にZyboと入力します。今回使用する基板は「Zybo Zynq-7010評価ボード(Board Rev.4)」ですので、一番下の[Zybo]を選択します。

選択が完了したら、[Next]をクリックしましょう。

私は、ここで間違って[Zybo Z7-10]を選んだまま、作業を続けてしまい、全く”Hello World”の文字列を受信することができませんでした…。

半日くらい原因がわからずに悩み続けてしまいましたので、設定は丁寧に行うことが重要です。

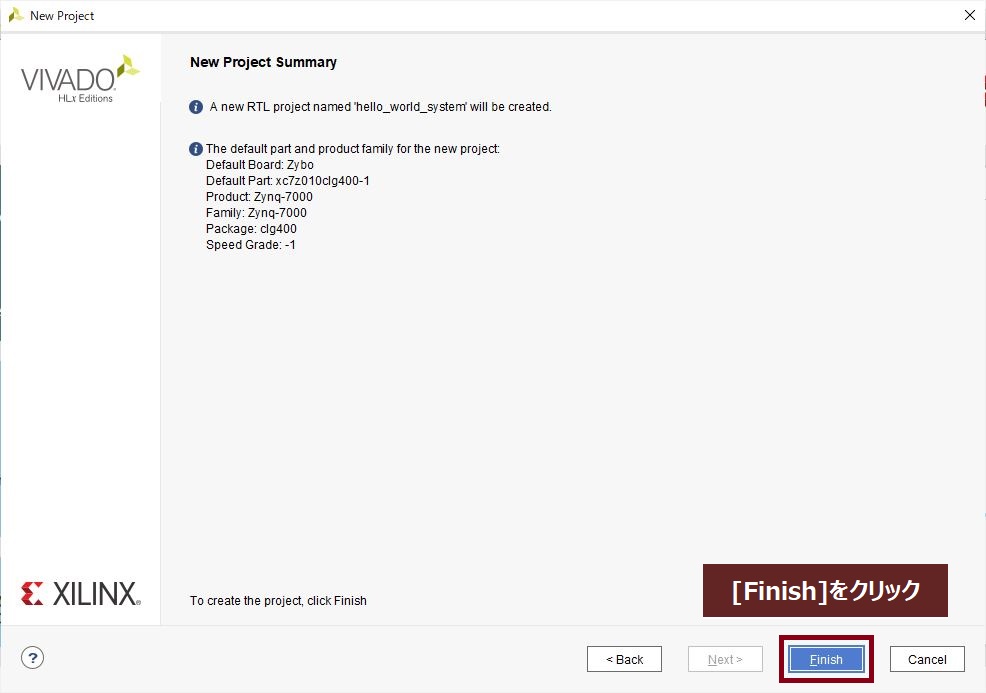

最後に、プロジェクトの設定のサマリが表示されますので、間違いがないことを確認したら、[Finish]をクリックしましょう。

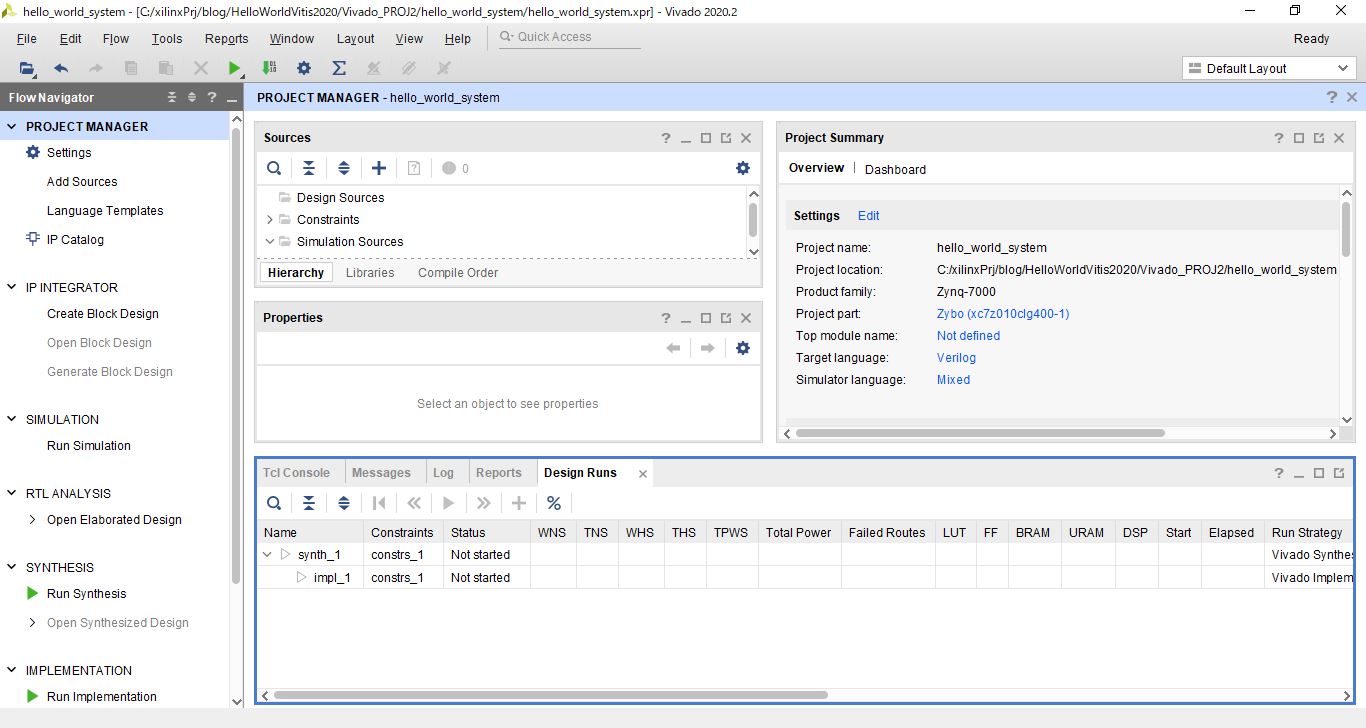

以上で、Vivadoのプロジェクトを作成することができました。

ブロックデザインの作成

次に、プロジェクト上で、Zynq SoCに実装する回路の設計を、ブロックデザイン上で行っていきます。

まず、左の[Project Manager]の[Create Block Design]を選択します。

そうすると、図のようなウィンドウが立ち上がります。

ここで、デザイン名とブロックデザインの設計ファイルを格納するディレクトリを指定します。

今回は、デザイン名を[hello_world_system]としました。入力が完了したら、[OK]をクリックします。

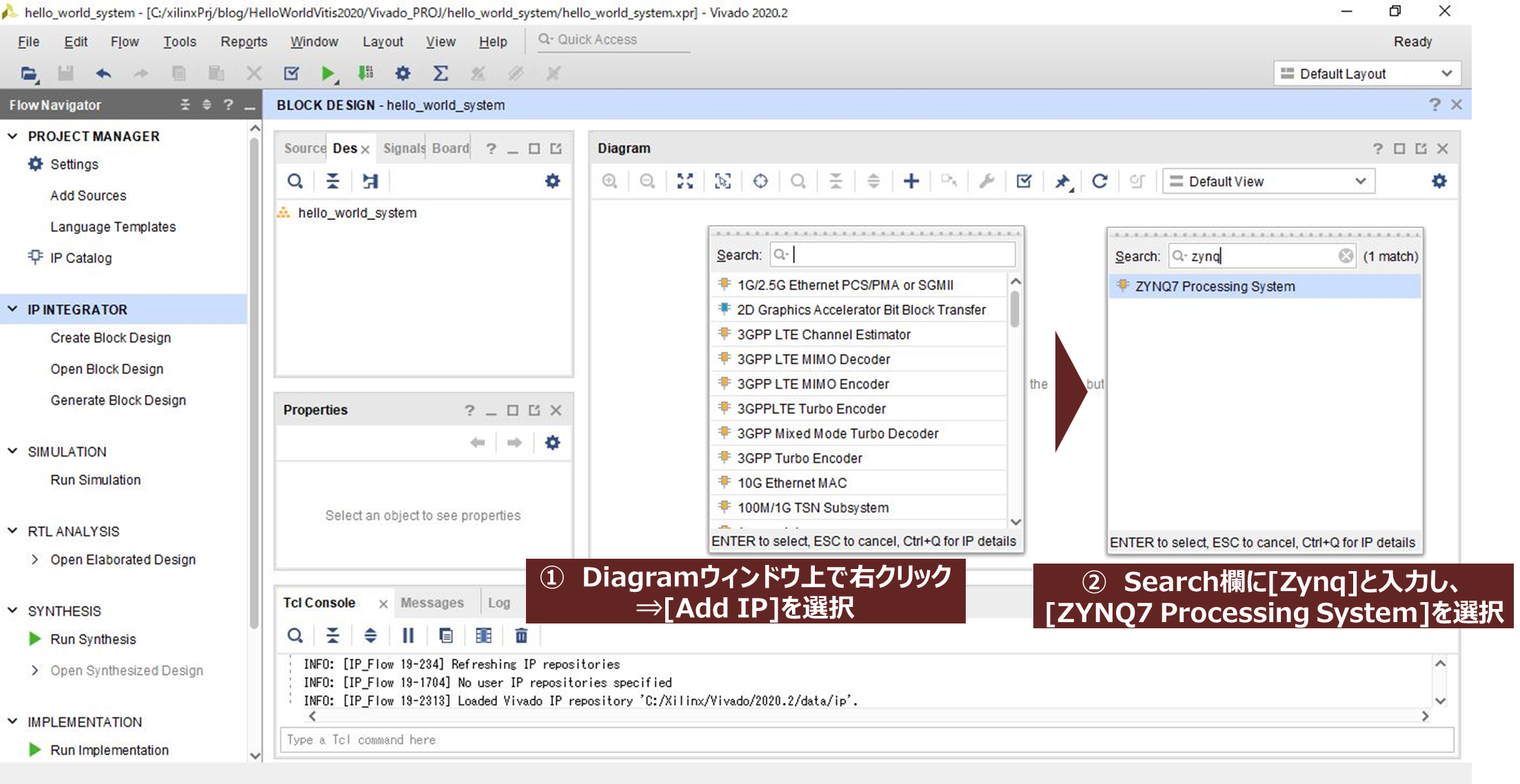

空白のDiagramウィンドウが開きます。このウィンドウにZynqのプロセッサコアを表すIPを追加していきます。

ウィンドウ内で右クリックをし、[Add IP]を選択します。Searchの画面が出てきますので、そこに[Zynq]と入力し、[ZYNQ7 Processing System]を選択します。

選択すると、図のようにZynqのプロセッサコアを表す “processing_system_7” という名前のIPが追加されます。

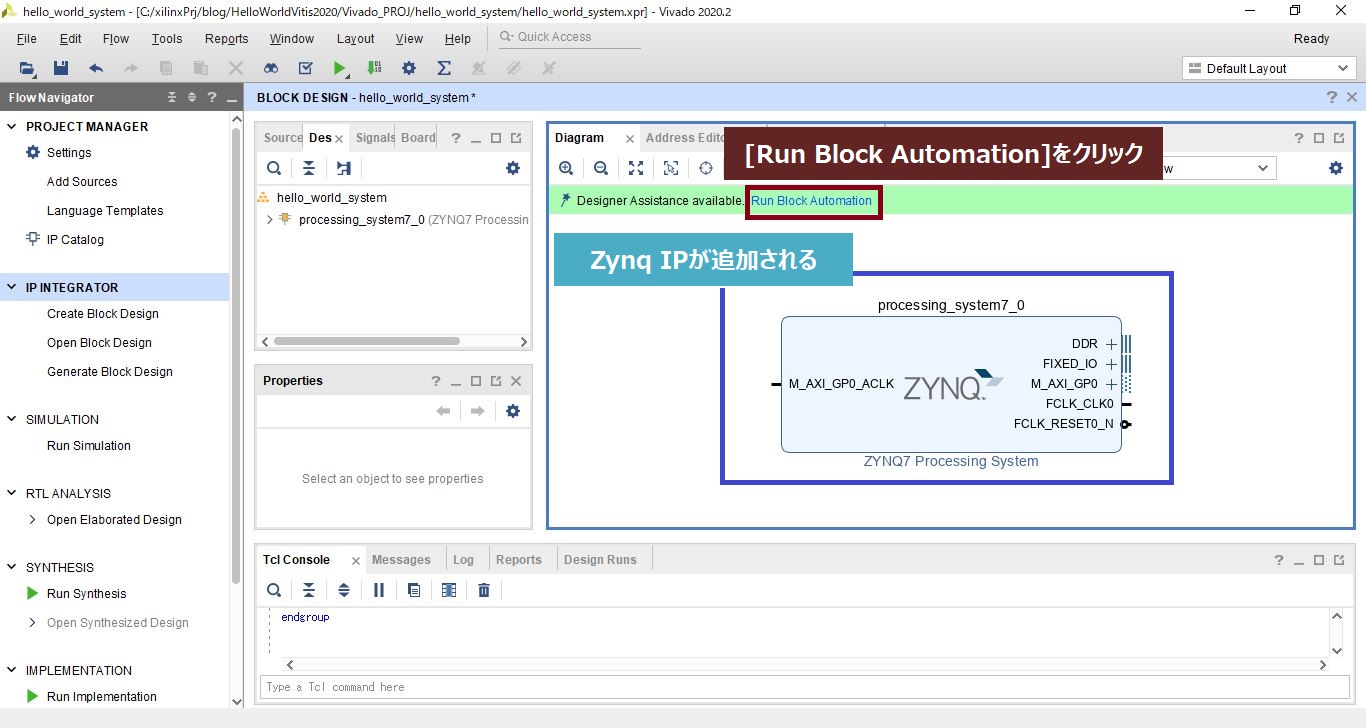

[Run Block Automation]をクリックし、自動でコアの設定をしていきましょう。

※Zyboのボードに関するファイルを読み込んでおかないとここで詰まりますので注意!

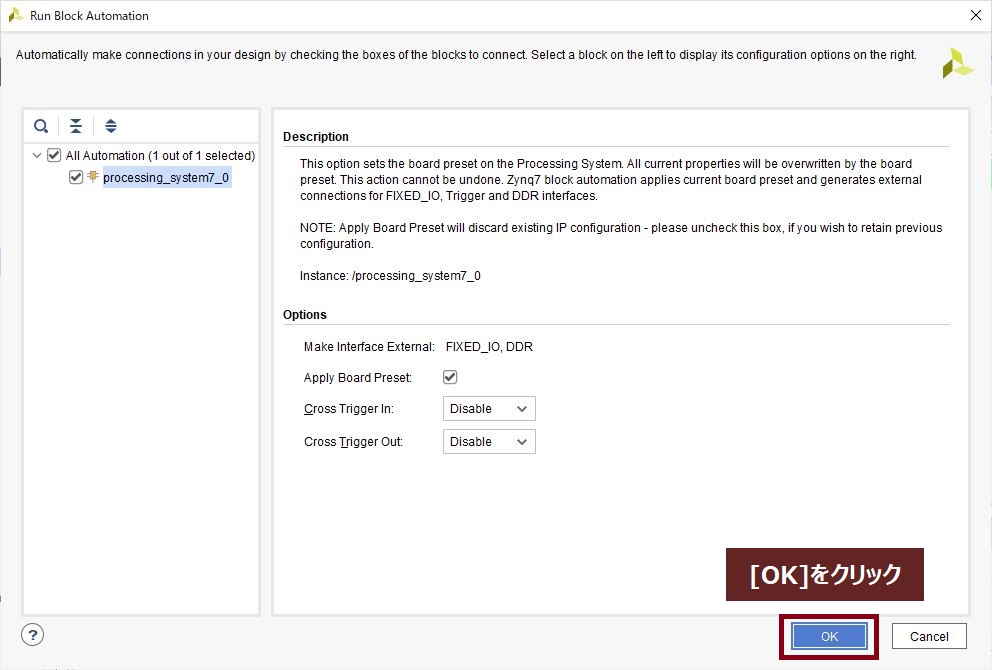

自動化の設定を決定するウィンドウでは、何も変更せず[OK]をクリックします。

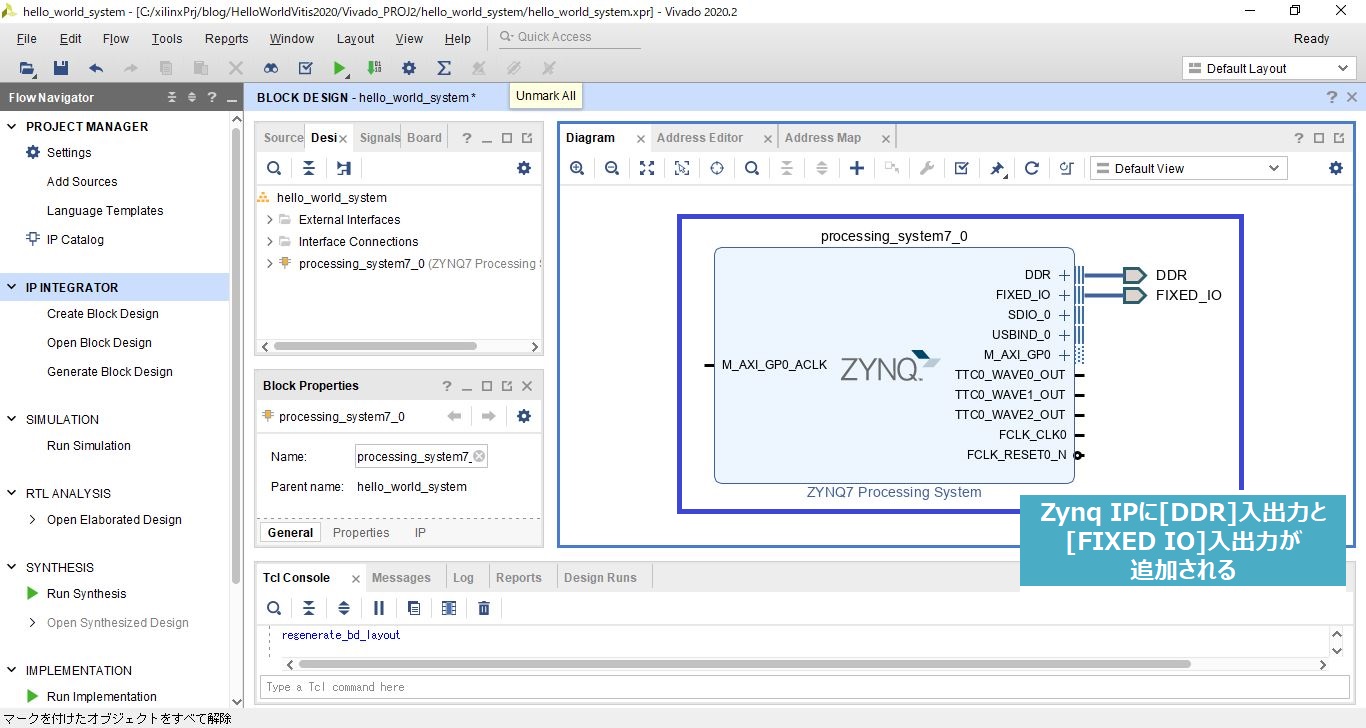

IP “processing_system_7″に接続ポート[DDR]と[FIXED_IO]が追加されます。

このポートを介してそれぞれボード上のDDRメモリと、イーサネットやUSBのような周辺回路との、信号の入出力を行います。

DDR … Zybo上のDDRメモリとの信号の入出力

FIXED_IO … イーサネットやUSBのような周辺回路との信号の入出力

FIXED_IOにおける周辺回路との接続を行うインターフェースは、MIO(Multiplexed I/O)と呼ばれています。

このMIOのうち、今回はホストPCに”Hello World”の文字列を送信するためのUARTのポートのみを使用します。

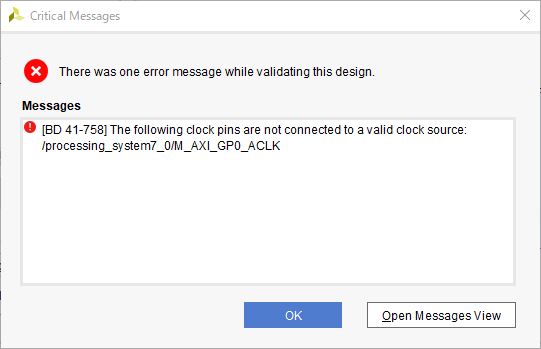

このブロックだけで、”Hello World”のプログラムを実行するのに十分なモジュールは揃っているのですが、このままダイアグラムをもとにHDLファイルを作ろうとするとエラーが発生します。

これはPL側との接続を行うAXI ポート”GP0″のクロック(M-AXI_GP0_ACLK)に何も接続されていないためです。

今回のテーマでは、PL側にロジックを組む必要はないので、AXI ポート”GP0″は使用しません。

このクロックも当然使用しませんが、エラー回避のため、図のように”FCLK_CLK_0”から”M-AXI_GP0_ACLK”へのクロック出力を繋ぐことで対処します。

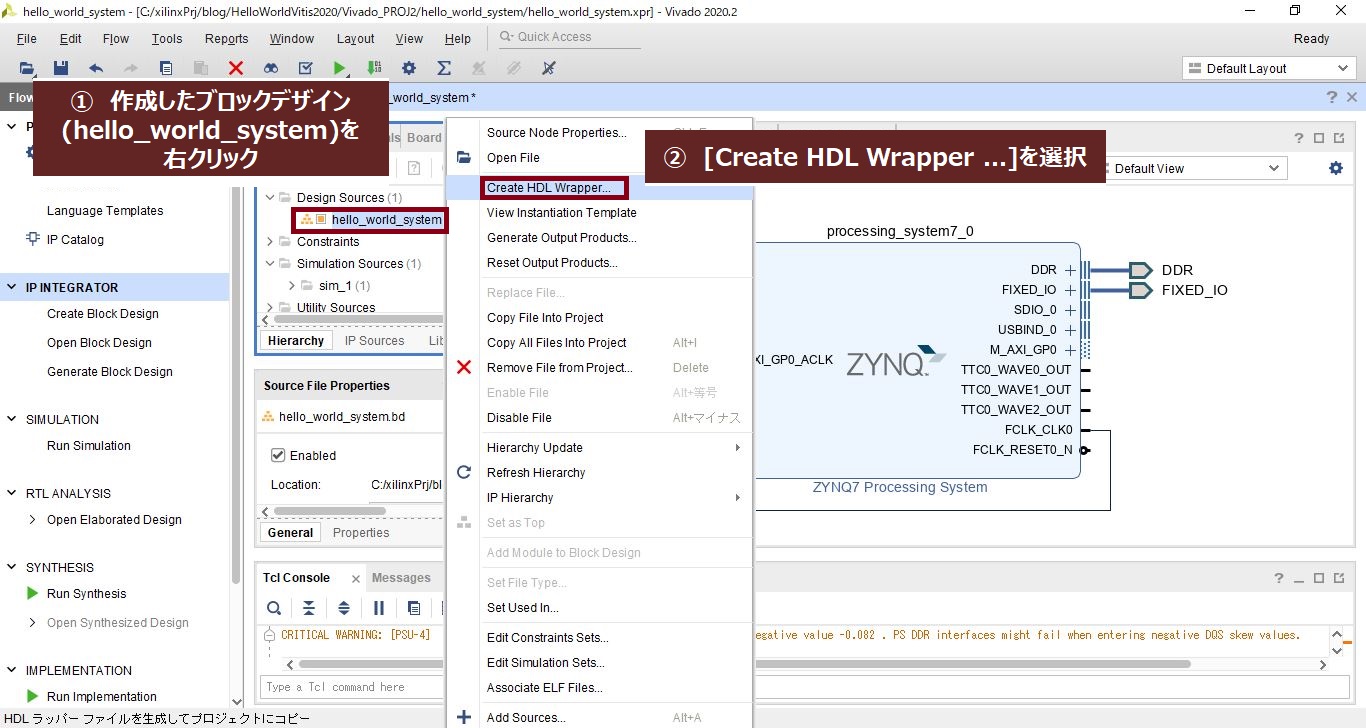

最後に、作成したブロックデザインに基づいて、設計をHDL言語で書かれたプログラムファイル(wrapperファイル)に変換していきます。

この変換も自動でVivadoが行います。

ちなみに、”FCLK_CLK_0”はPLにクロックを提供する目的でPS側から出力されています。PSにおけるクロックはボード上に搭載されている振動子50MHzをもとに生成され、そのクロックがCPUやDDR、内蔵周辺回路、そしてそれを分周したものをPL側に提供しているようです。

作成したブロックデザイン(今回はデザイン名”hello_world_system”)を選択し、右クリックし、[Create HDL wrapper …]を選択します。

そうすると、図のようにwrapperファイルが作成されます。

これでブロックデザインの作成は完了です。

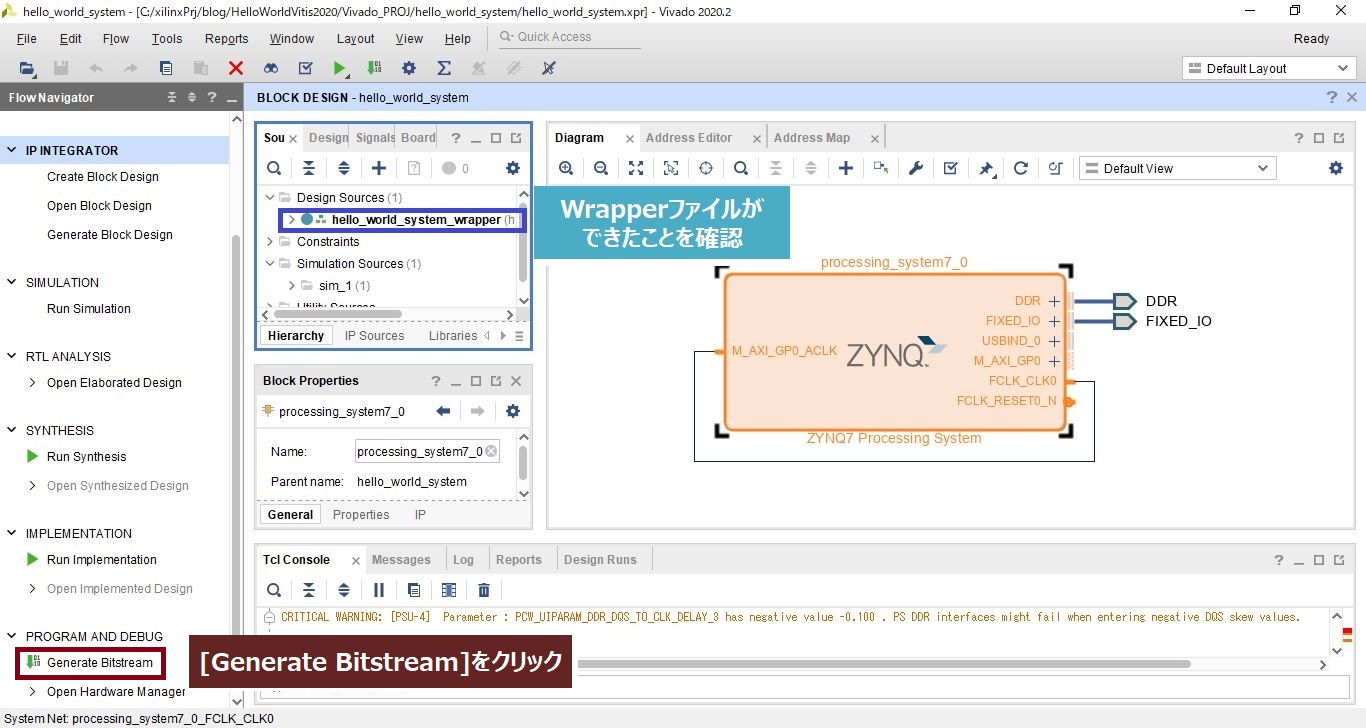

論理合成、配置配線、bitstreamファイルの作成

作成したHDLファイル(“hello_world_system_wrapper”)から、論理合成・配置配線、そしてFPGAに実装するためのbitstreamファイルの作成までを行います。

左の[Project Manager]の[Generate Bitstream]をクリックします。

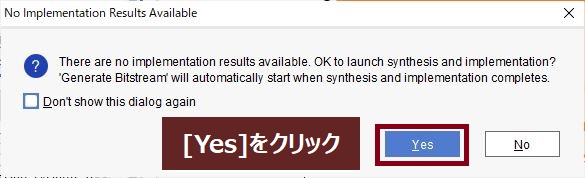

次のようなウィンドウが出てきますが、そのまま[Yes]をクリックします。

次の画面も、[OK]をクリックします。

そうすると、Vivado上で順次論理合成、配置配線、bitstream作成が行われます。

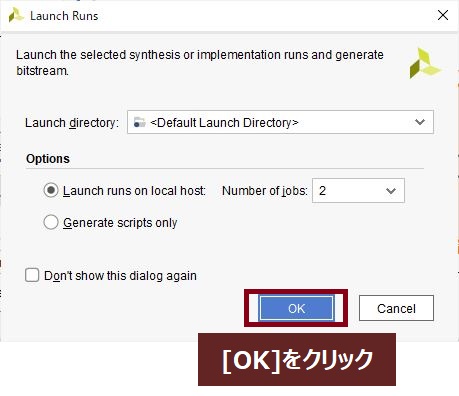

bitstreamの作成が完了するまでに数分ほど時間がかかります。

作成が完了すると、次のような作成完了のウィンドウが立ち上がります。今回、特にレポート等の確認はしなくてもよいので、そのまま[Cancel]でウィンドウを閉じます。

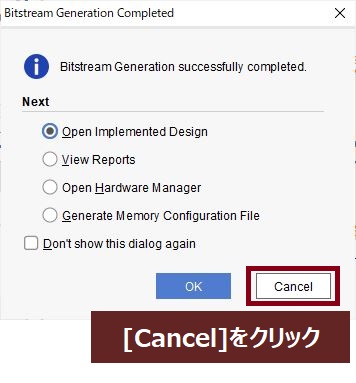

ハードウェアデザインのエクスポート (XSAファイルの作成)

bitstreamファイルによりZynq SoCに実装する回路設計図ができました。

次に、Vitisでプラットフォームプロジェクトを作成していくのに必要な、ハードウェアデザインをエクスポートしていきます。

このときエクスポートされるファイルはXSAファイルと呼ばれます。

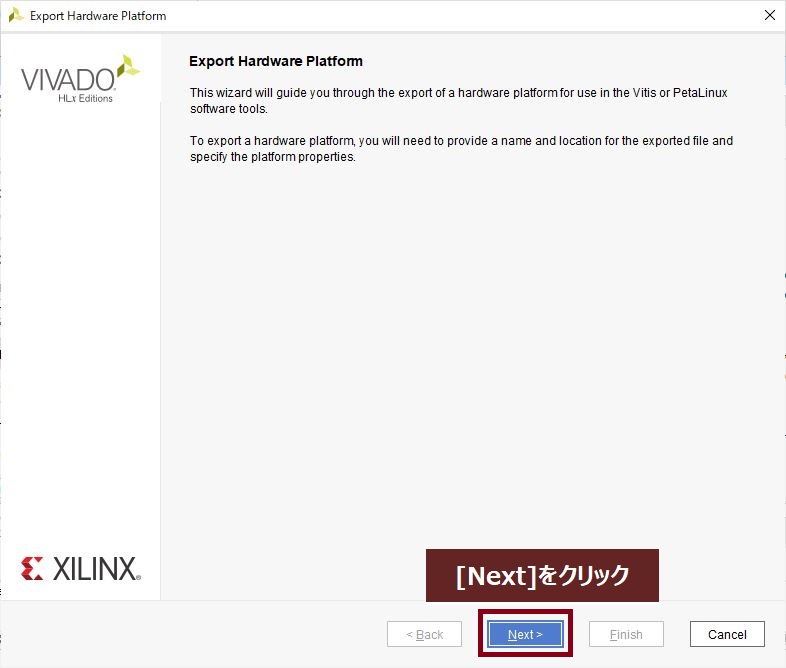

Export Hardware Platformというウィンドウが立ち上がりますので、[Next]をクリックします。

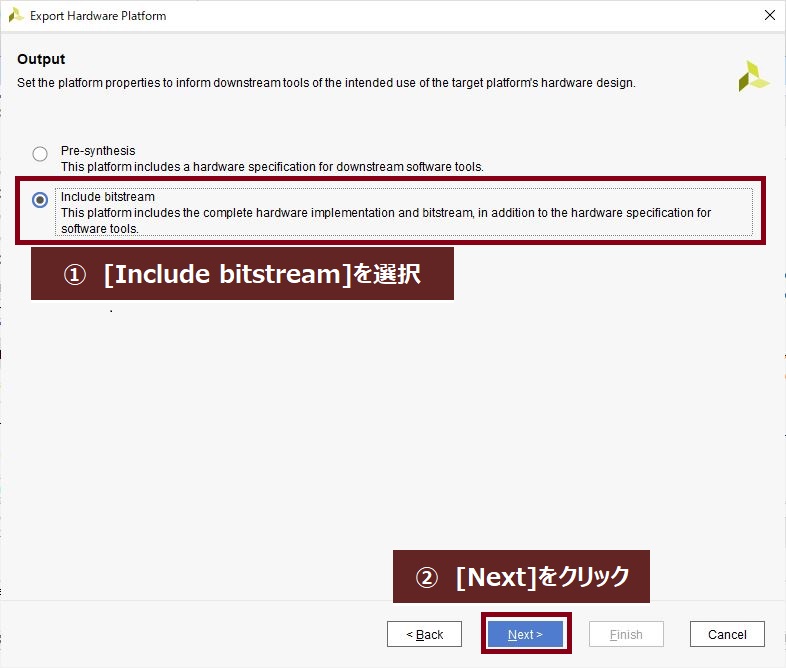

ハードウェアデザインにbitstreamファイルを含めるかどうか選べます。ここでは、[Include bitstream]を選択し、[Next]をクリックします。

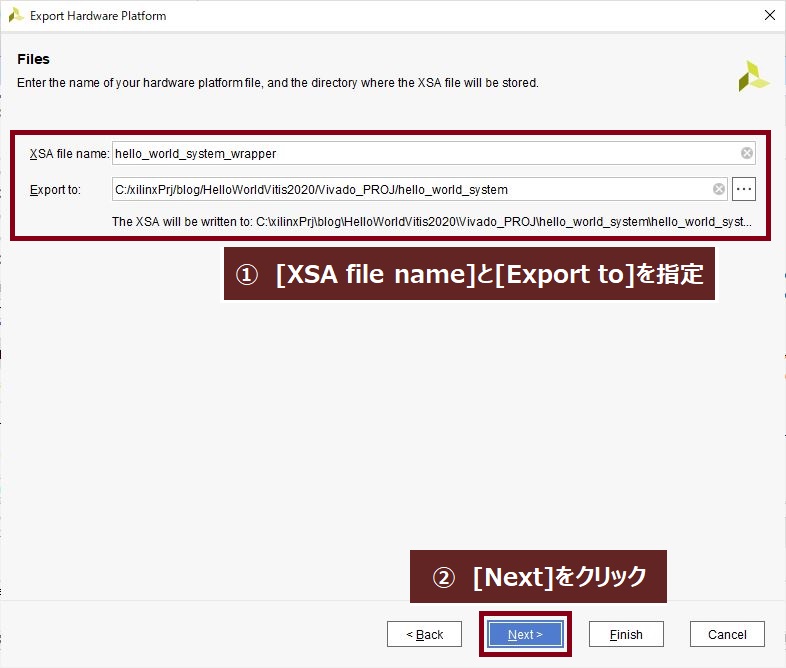

次に、XSAファイル名と格納するディレクトリを指定します。

今回は、ファイル名を[hello_world_system_wrapper]としました。入力が完了したら、[Next]をクリックします。

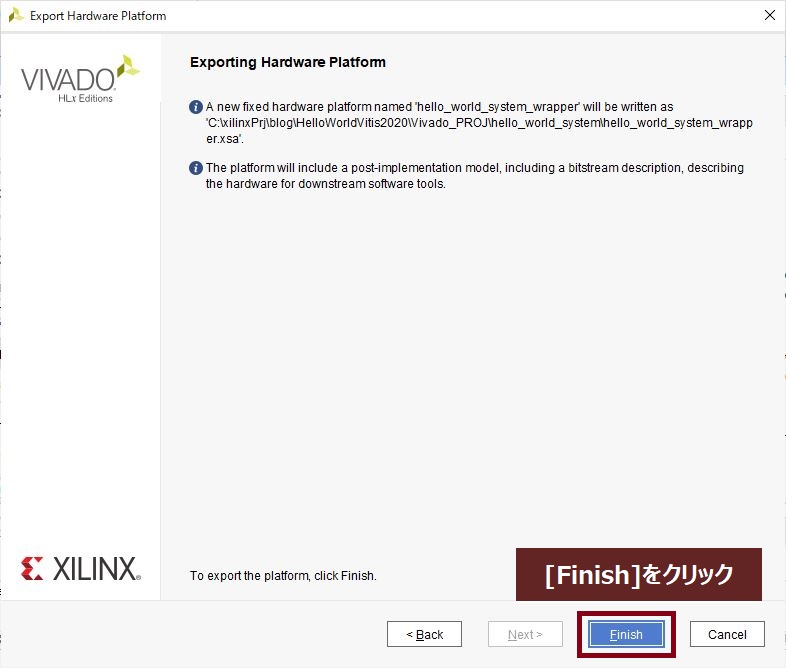

最後に、設定を確認し、間違いがなければ、[Finish]をクリックします。

この作業までで、赤枠のPSのハードウェアの構築までが完了しました。

あとは、ソフトウェア側の構築、つまりCPUを動かすためのプログラムを作成するだけです。本日の記事を踏まえて”Hello World”プログラムの作成と実装を、次回Vitis 2020.2上で行います!

まとめ

“Hello World”プログラムをFPGAに実装するためのブロックデザインをVivado 2020.2上で作成。ブロックデザイン上で以下のIPを配置した:

- プログラムを実行するためのCPUが搭載されたFPGA Zynq

- プログラムを格納するためのDDRメモリとの入出力ポート

- 信号を送信するホストPCとのUART出力ポート

コメント