本記事の概要

VerilogやVHDLなどのハードウェア言語を用いて作成したRTLモジュールの入出力に、IPパッケージャーを使用してAXI4-Liteインタフェースを追加する方法を解説。

本記事では、VivadoからカスタムIPを作成する手順を説明。

Xilinx社で提供されるIPのインターフェースは、AXI(Advanced eXtensible Interface)と呼ばれるプロトコルで共通化されています。

AXIとは、ARM社が公開しているバス規格AMBA(Advanced Microcontroller Bus Architecture)の仕様の一部です。

2010年にリリースされたAMBA4.0には、特徴の異なる3種類の仕様で構成されるAXI4が含まれています:

- AXI4:メモリマップ方式の高性能インターフェース。大容量・高速伝送

- AXI4-Lite:簡素化され単一データの転送のみ可能。制御レジスタ・ステータスレジスタとの通信に使用。

- AXI4-stream:AXI4同様に大容量・高速伝送が可能なデータストリーミング用。アドレスを持たず連続データのみ転送。AXI4に比べて、比較的制御が容易。

Xilinx社では、IPコアのインタフェースにAXI4プロトコルを採用することによって、システム開発での生産性・互換性・柔軟性を高めています。

- 生産性:開発者が理解すべきプロトコルがAXI4のみでよい。

- 可用性:IPを変えてもインターフェースが共通なので接続が楽。サードパーティにとってもAXI4インタフェースを持つようにIPを提供すれば普及しやすい。

- 柔軟性:アプリケーションで送受信するデータ容量や速度によって3種の仕様を選択できる。

つまり、AXI4はXilinx社のIPを使う上での共通言語の役割を果たしています。

AXI4プロトコルの動作について学ぶには以下の書籍がおすすめです。入門者向けにAXI4プロトコルの動作は、「FPGAプログラミング大全」に非常にわかりやすく解説されています。

一方、AXI伝送の動作を理解しても、実際にIPにAXIプロトコルの入出力インターフェースを追加するのは大変です。

私はVerilogやVHDLで記述したRTLモジュールのコーディング作業中、Xilinxが提供するIPに接続するためにAXIインターフェースを自前で用意するのは正直面倒でした。

実際、Xilinx社が提供するVivadoやVitisには、開発者がゼロからハードウェア記述言語でインタフェースを設計し、コーディングしなくても済むようなツールが実装されています。

開発者が所望の機能を満足するシステムの開発に注力できるように、サポートをしているということがわかります。

今回は、VivadoのIPパッケージャーを使用して、カスタムIPにAXI4-Liteインタフェースを追加する方法を解説します。

まずは、S側のインタフェースを追加します。受動的に動作するS側のほうがM側よりも理解しやすいためです。

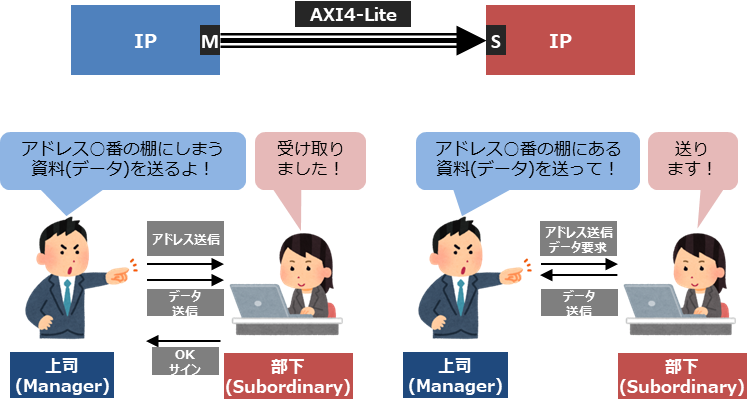

AXI4プロトコルでは、2つのIP間でデータの送受信を行うときに、一方のIPが送受信の主導権を握り、もう片方のIPを制御・操作する決まりとなっています。

主導権を握って制御・操作する側にはM、される側にはSという接頭辞をつけています。MはMasterやManager、SはSlaveやSubordinaryなどの略称です。

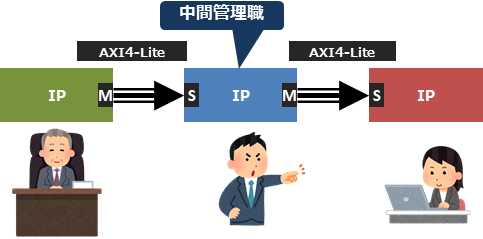

ちなみに、実際の社会でも課長のうえに更に部長や社長のような上司がいて、人との関係によって立場が変わるように、S/Mの立場は2つのIPの組み合わせによって変わります。

下の図のようなIPの接続では、真ん中のIPは左のIPに対しては従属的なSの役割をしますが、右のIPに対しては主導権を握るMの役割をします。

いわゆる、中間管理職ですね。

次回以降の記事では、このカスタムIPの内部構成の解説、そして、カスタムIPを動かすドライバAPIの使用方法を解説し、Zynq上のプロセッサで動作確認を行います。

- 自作RTLモジュールの接続先IPにAXI4インタフェースしか用意されていないような場合

- カスタムIPに制御レジスタやステータスレジスタを設け、プロセッサからそれらを参照したい場合

目標

本記事全体の目標は次の通りです:

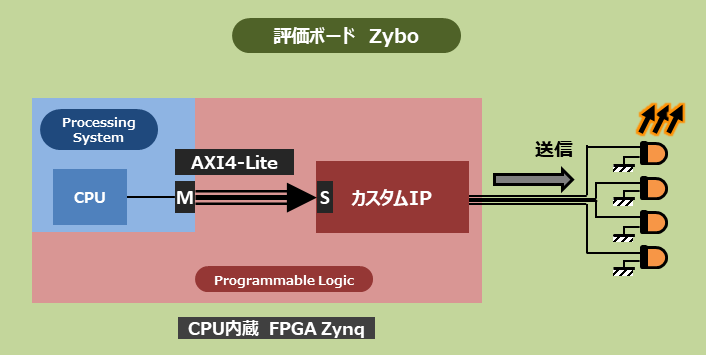

自作のRTLモジュールにAXI4-Liteインタフェース(S側)を追加する

カスタムIPに実装するRTL回路は比較的簡単なLED点滅回路とします。

プロセッサが書き込んだ制御レジスタの値によって、LEDの点滅位置を変更します。

IPパッケージャーの使用方法

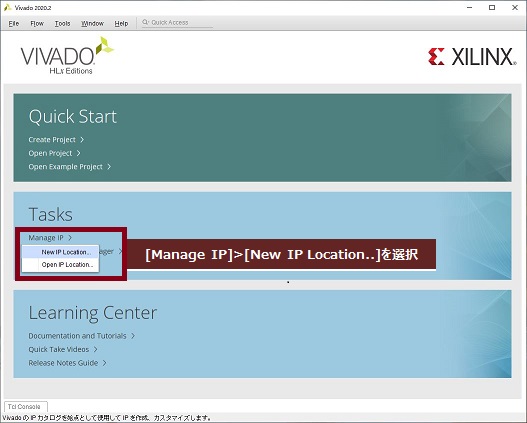

では、IPパッケージャーを使って、カスタムIPを作成していきましょう。

IP管理プロジェクトの作成

まず、Vivadoを立ち上げ、Tasks内の[Manage IP]>[New IP Location..]を選択します。

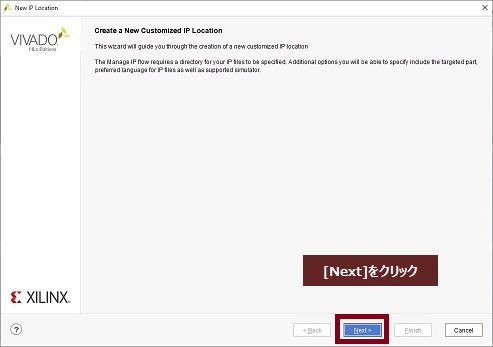

新しくウィンドウが立ち上がります。新しく作成するカスタムIPの格納先のパスを指定するウィンドウです。そのまま[Next]をクリックします。

カスタムIPを作成するに当たり、対象とするFPGAチップやボード、使用言語、シミュレータを選択します。

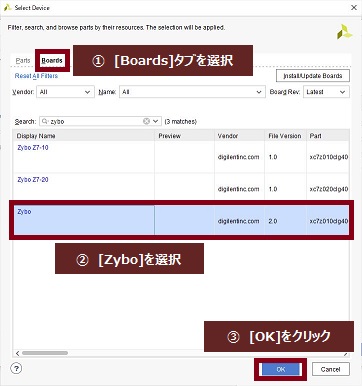

FPGAチップを変更しましょう。Partの[…]をクリックすると、新しくデバイスを選択するウィンドウが立ち上がります。

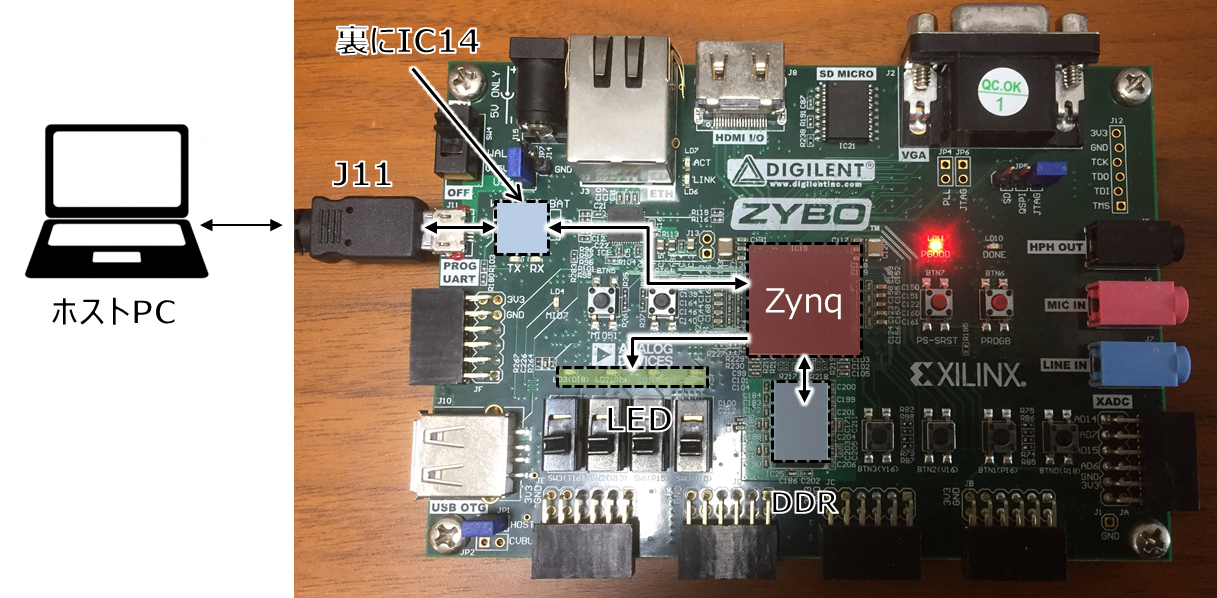

今回は、ZynqボードのZyboを実装対象としますので、[Boards]タブを選択し、[Zybo]を選択します。

各々が使用しているFPGAチップやボードを選択ください。

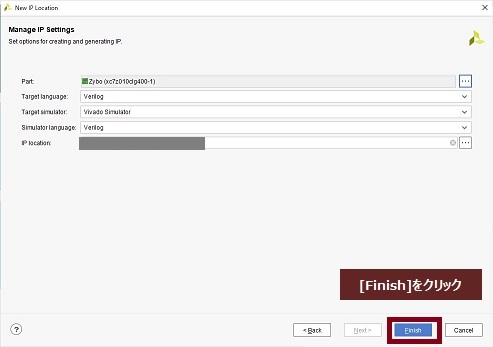

また、使用言語は[Verilog]を指定しました。VHDLに慣れている方は、ここで[Target Language]や[Simulation Language]を変更すると良いでしょう。

設定が完了したら、[Finish]をクリックします。

以上で、IPを管理するVivadoのプロジェクトの作成は完了です。

カスタムIPの作成

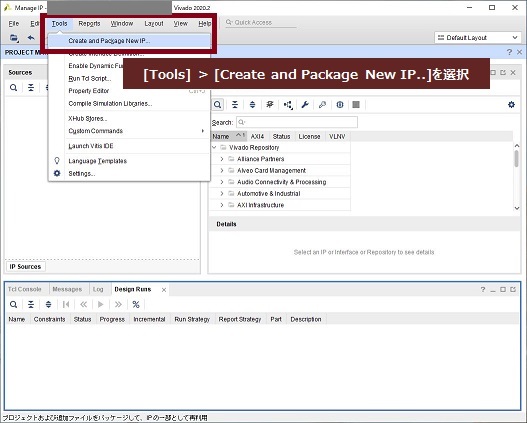

次に、カスタムIPを作成するために、[Tools]>[Create and Package New IP..]を選択します。

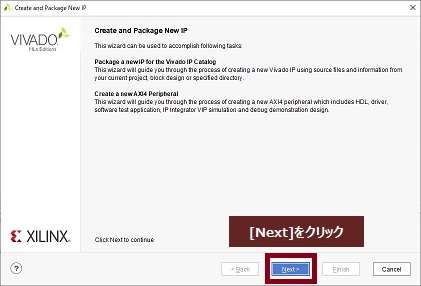

新しくカスタムIPを作成するIPパッケージャーが立ち上がります。そのまま、[Next]をクリックします。

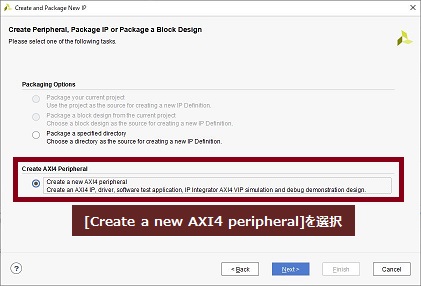

カスタムIPの雛形を指定するためのウィンドウです。

今回は、AXI4のインターフェースを持ったカスタムIPを作りたいので、[Create a new AXI4 peripheral]を選択します。

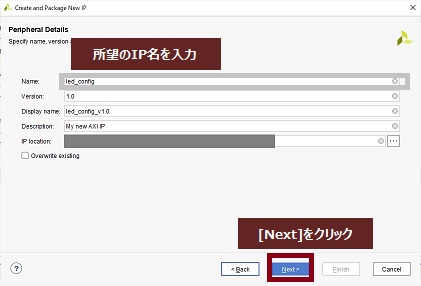

カスタムIPの詳細を決めるウィンドウです。Name欄に所望のIP名を入力しましょう。ここでは、[led_config]としました。

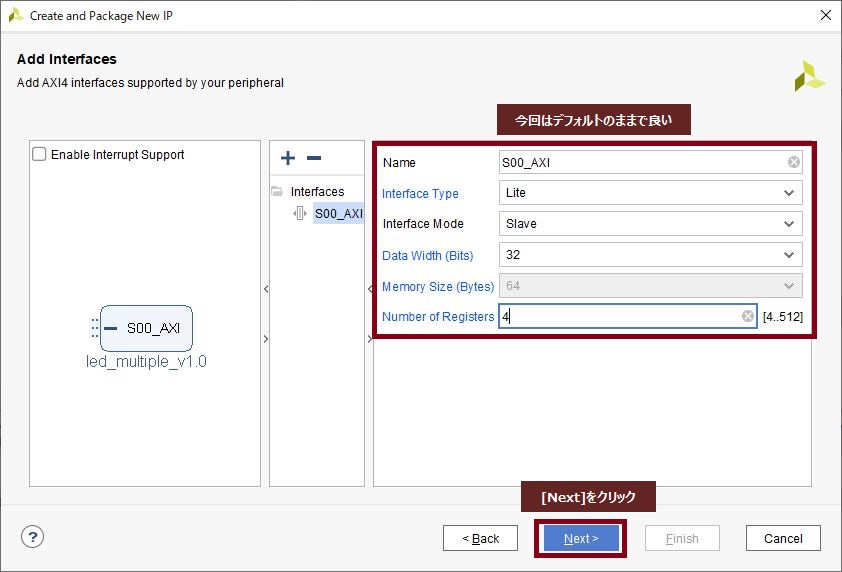

入出力に作成するAXI4インターフェースを追加するウィンドウです。

ここでは、S側のAXI4-Liteがデフォルトで設定されています。例えば、M側のAXI4-Liteを追加したり、AXI4-streamに変更したり、設定を変えることが可能です。

今回は、デフォルトのままで良いですが、各々が作成したいカスタムIPに応じてインターフェースをカスタマイズできます。

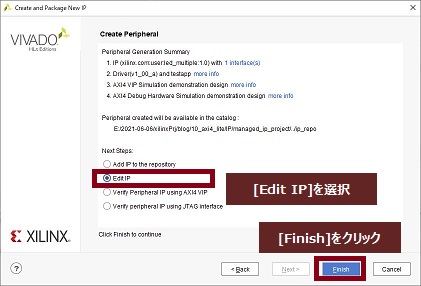

最後のウィンドウです。[Edit IP]を選択し、IPの中身を書いていきましょう。

ちなみに、[Add IP to the repository]を選択しても、あとからIPを変更可能なので、一旦レポジトリに追加してしまってもよいです。

以上で、カスタムIPの雛形の作成は完了です。

作成したIPのフォルダ内部に雛形となるHDL記述のファイルが格納されています。

- パス:[..\IP\ip_repo\led_config_1.0\hdl]

- ソースコード:

- led_config_v1_0.v

- led_config_v1_0_S00_AXI.v

今回は使用言語にVerilogを指定したので、これらのソースコードはVerilogで記述されています。

まずは、本記事でカスタムIPを作成しました。次回の記事では、内部の構成を解説したあとに、どこを具体的に変更すればよいかを解説しようと思います。

最後までご覧いただきありがとうございました!

次回の記事へのリンク

参考:コードの動作を確認したシステムの構成

開発環境

- 開発用PC: Windows 10, 64bit

- Vivado Design Suite – HLx Edition – 2020.2

- Vitis コア開発キット – 2020.2

- 開発用基板: Zybo Zynq-7010評価ボード(Board Rev.4)

- Zynq XC7Z010-1CLG400C

開発ボード Zybo Zynq-7010評価ボード

コメント