本記事の概要

- Xilinx ソフトIPコアAXI VDMAの基本機能について解説

- AXI VDMAは、メモリと周辺機器とのビデオ信号のやり取りをDMA方式で行うためのIPコア

- AXI VDMAには、3種類の主要なインターフェースが用意され、他のIPコアとは以下の通り接続する

- AXI4 Memory Map :メモリに接続されるビデオデータの伝送バス

- AXI4-Stream : 周辺機器(ペリフェラル)に接続されるビデオデータの伝送バス

- AXI4-Lite:AXI VDMAコアの制御信号やステータス信号の伝送バス

過去の記事では、「Vitis」でのビジョンライブラリを試す前準備として、Digilent社が提供するHDMI出力デモのサンプルプログラムを読み込み、自動でビデオ生成に有益なIP類が追加されました。

中でもビデオ生成において、DDR3メモリからデータを読み出し、AXI4形式で出力させるAXI Video Direct Memory Access (VDMA)コアは、ビデオ生成部における中核をなすIPとなっています。

しかし、使える機能が多様な分、説明が多く、初心者には敷居の高いIPと感じます。

そこで、まず最初に使うにあたって、最低限知っておくと良い項目についてまとめました。

- FPGAの開発に興味のある学生

- Vitisを用いたアプリケーション開発は未経験のエンジニア

- FPGAでの動画像処理を行いたいエンジニア

それでは、興味のある方はぜひ最後までご覧ください!

AXI VDMA(Video Direct Memory Access)の機能

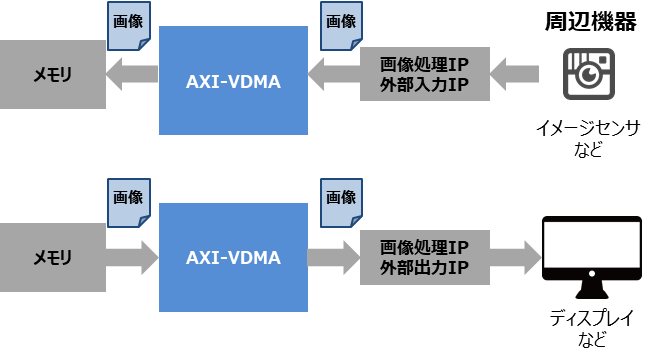

AXI Video Direct Memory Access (AXI VDMA) コアとは、ビデオ入出力を行う周辺機器(ペリフェラル)とメモリとを、直接つなぐIPコアです。

周辺機器は、例えば、カメラなどからのビデオ入力や、HDMIケーブルを通じた外部ディスプレイへのビデオ出力などの、ビデオインターフェースをイメージすると良いかと思います。

基本的には、メモリとビデオインターフェースとの間に配置して、メモリとの画像の送受信を高効率に行うためのIPコアといえます。

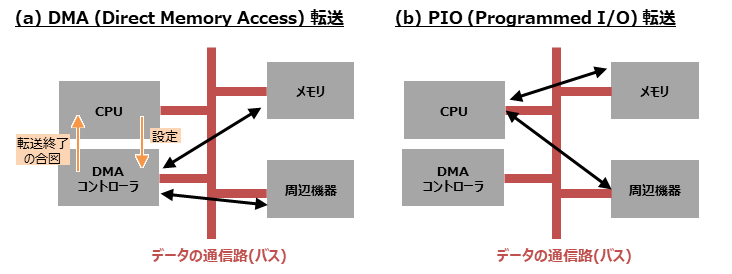

DMA (Direct Memory Access) 方式

高効率にアクセスできる理由は、DMA (Direct Memory Access)方式を採用し、CPUを介さずに直接、メモリと周辺機器(ペリフェラル)とを接続して、メモリへの書き込みと読み出しを行っているためです。

通常、データをメモリに書き込んだりメモリから読み出したりする作業は、CPUが行います。この方式は、PIO (Programmed I/O)方式と呼ばれます。

しかし、メモリへの書き込み・読み出しの処理中には、CPUは他の処理を効率的に行うことができません。

そこで、DMA方式と呼ばれる、周辺機器(ペリフェラル)とメモリとを直接接続し、CPUを介さずにデータの書き込み・読み出しをできるようにしています。

ビデオや音声などの大量かつ継続的にデータをメモリに入出力したい場合には、DMA方式を採用するほうが、結果的に処理性能を向上することが可能です。

- 高速性・大容量性(周辺機器とメモリ間の高速かつ大容量にデータ転送可)

- CPUの負荷軽減(CPUはメモリ伝送以外の別のタスクに集中可)

一方、メモリ・周辺機器・CPUなどの複数の端末が、一つのデータバス(データの通信路)を共有しているので、バス使用権の調整を行うDMAコントローラを配置しなければいけません。

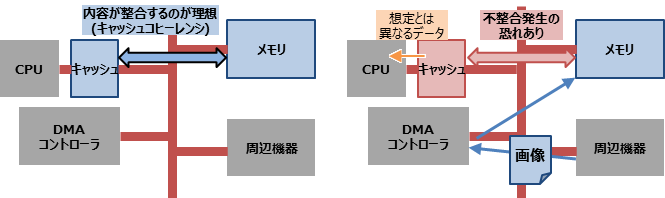

また、キャッシュコヒーレンシの問題が起こる可能性もあります。

CPUはメモリと読み出し・書き込みを行う際に、一時的にキャッシュと呼ばれるデータアクセスが早い領域に一旦データを溜め込んでおき、処理を行います。このとき、メモリの内容とキャッシュの内容の整合性(コヒーレンシ)をとることを、キャッシュコヒーレンシと呼びます。

DMA方式では周辺機器がメモリと直接アクセスできてしまいます。

そのため、キャッシュとメモリの整合性を取る前に、CPUがキャッシュにアクセスしたり、あるいは周辺機器がメモリにアクセスしたりしたときに、想定とは異なるデータが送受信されてしまう恐れがあります。

- DMAコントローラを配置する必要がある

- キャッシュコヒーレンシの不整合発生の懸念

DMA方式は、多少のデメリットはありますが、大容量のデータを高速にやり取りする際には、採用するメリットのほうが多い方式といえます。

特に、ビデオ入出力の用途では、大容量の画像データを高速にメモリとアクセスする必要があるため、メモリと直接アクセスできるDMA方式を採用するのが良いでしょう。

AXI VDMAコアは、ビデオ入出力向けにDMA方式でメモリとアクセスできるようにしています。

DMA方式は、以下の書籍で勉強しました。DMAに限らず、汎用的に使われるペリフェラルの通信方式からマイコンやRaspberry Piを使ったシステムの例が初学者向けにわかりやすく書かれた、おすすめの書籍です。

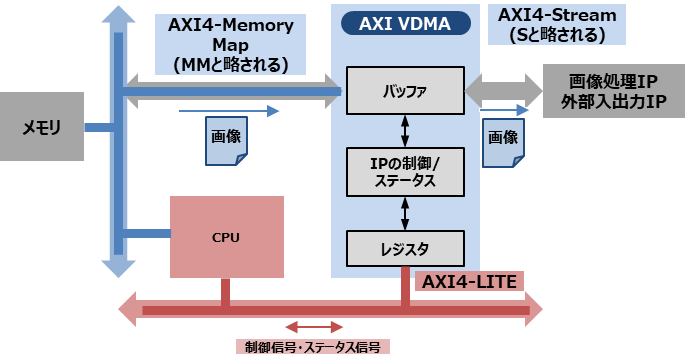

AXI VDMAの接続方法

AXI VDMAにおけるインターフェース

AXI VDMAコアには、他のIPコアとデータをやり取りするために、3種類の主要なインターフェースが用意されています。

- AXI4 Memory Map (MM):メモリに接続されるビデオデータの伝送バス

- AXI4-Stream (S) : 周辺機器(ペリフェラル)に接続されるビデオデータの伝送バス

- AXI4-Lite:初期化や割り込みなどAXI VDMAコアの制御信号やステータス信号の伝送バス

周辺機器と接続されるIPコアとはAXI4-Stream (S)と呼ばれる伝送バスで、メモリとはAXI4-Memory Map (MM)と呼ばれる伝送バスで接続します。

画像データはこの伝送バスを通じて、メモリと周辺機器との間で送受信されます。

また、初期化や割り込みなど、制御信号やステータス信号をCPUとやり取りするときには、AXI4-LITEと呼ばれる伝送バスを通じて行われます。

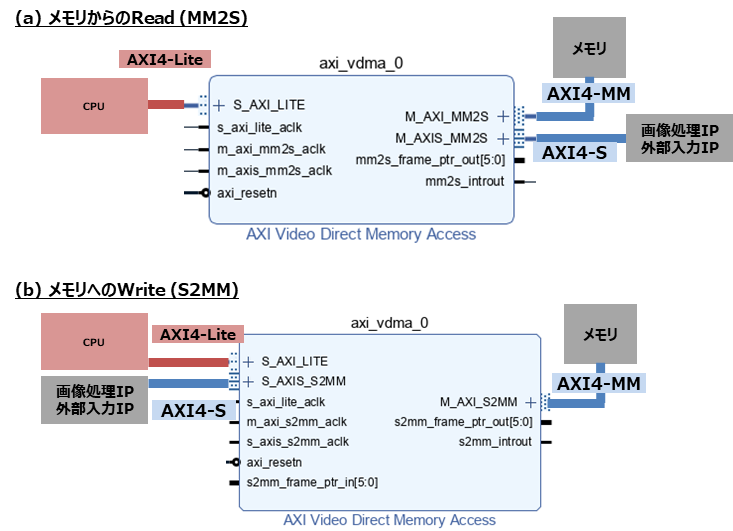

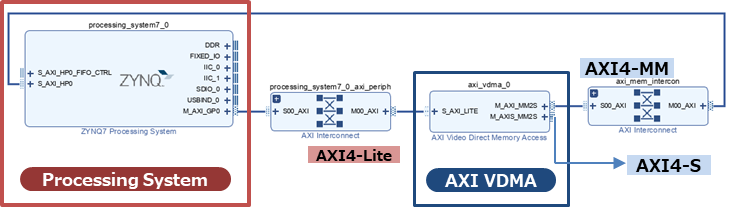

実際のVivadoにおけるブロックダイアグラム上でIPコアを確認してみましょう。

IPの設定画面上で、メモリからの読み出し(Read)と、メモリへの書き込み(Write)のいずれを行うのかを(あるいは両方を)設定することが可能です。

今回は、ReadとWriteの各設定をした場合の、IPのブロックダイアグラムを示しました。

各バスの接続方法を表にまとめると、この通りです。

| 方向 | メモリ(MM)側と 接続するバス | 周辺機器(S)側と 接続するバス | 制御・ステータス信号を やり取りするためのバス |

| メモリから読み出す (Read方向) | M_AXI_MM2S | M_AXIS_MM2S | S_AXI_LITE |

| メモリに書き込む (Write方向) | M_AXI_S2MM | S_AXIS_S2MM | S_AXI_LITE |

接頭辞のM_やS_というのは、そのIPが送受信を行う場合に、マスター側になるか、スレーブ側になるか、という役割分担を示しています。

マスター側が主導権を握って、スレーブ側が指示に従ってデータを受信したり、送信したりするわけですね。

メモリから読み出す場合(Read)、Memory Map(MM)からStream(S)へ画像データを伝送することになるので、MM2Sと略されています。

IP上にはMM2Sが名前に含まれるインターフェースは2つあり、一つがM_AXI_MM2S、もう一つはM_AXIS_MM2Sです。

AXIの後に「S」がついているだけの違いですが、M_AXI_MM2Sの方はMM側、すなわちメモリに、M_AXIS_MM2SがStream側、すなわち周辺機器と接続されます。

そして、この2つ以外にS_AXI_LITEというインターフェースがあります。これが、CPUと制御信号・ステータス信号をやり取りするためのインターフェースとなります。

メモリへ書き込む場合(Write)は、逆にStream(S)からMemory Map(MM)へ画像データを伝送することになるので、S2MMと略されています。

こちらも読み出し(Read)と同様に、M_AXI_S2MMの方はMM側、すなわちメモリに、S_AXIS_S2MMがStream側、すなわち周辺機器と接続されます。

Zynq-7000におけるAXI VDMAの構成例

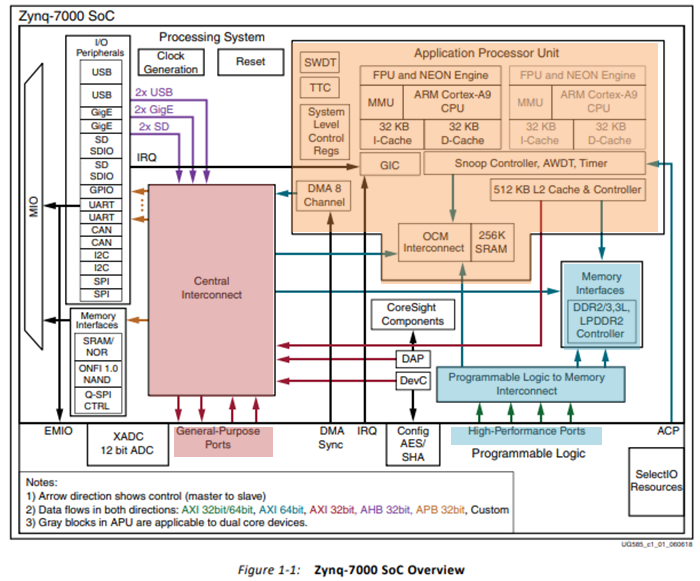

Xilinx SoCのZynq-7000を例に、ブロックデザインにおけるAXI VDMAの接続例を示したいと思います。

Xilinxが公開している、Zynq-7000の内部構成は以下のとおりです。

APU (Application Processor Unit)とPL (Programmable Logic)に2種類のインターコネクトが用意されています。

右のインターコネクトは、High-Performance Ports (HPポート)を通じて、DDRメモリとPL (Programmable Logic)との間で、データの送受信を行うことが可能です。

一方で、左のインターコネクトは、General-Purpose Ports (GPポート)を通じて、CPUとPLとの間で、データの送受信を行うことが可能です。

Zynq-7000 SoCのテクニカルリフェレンスから、各ポートのスループットと推奨する使用方法について調べました。

| 手段 | 推奨する使い方 | スループット(Estimated) |

| PL AXI_HP DMA | 大容量のデータセットをDMA形式で伝送 | 1,200 MB/s (複数のインタフェースそれぞれ) |

| PL AXI_GP DMA | ・PLとPS間の制御信号の伝送 ・PS I/O ペリフェラルのアクセス | 600MB/s |

この比較表によると、以下のように設定するのが良いかと思います。

- ビデオの送受信は大容量かつ高速な伝送が求められるので、AXI4 Memory MapはHPポートに接続

- 制御信号やステータス信号をやり取りするAXI4-LITEのバスはGPポートに接続

例えば、メモリからビデオ信号を読み出す場合、IPは図のような構成になります。

PS部とAXI VDMAの間にインターコネクトを配置し、AXI VDMAの制御信号やステータス信号はM_AXI_GP0ポートから、ビデオ信号はS_AXI_HP0ポートから入出力を行います。

ちなみに、AXI VDMA側から、メモリにデータを要求するので、AXI VDMAがマスターの役割をします。

DMA方式では、CPUはデータの送受信に関して基本的に何もできないので、AXI VDMAのMemory MapはRead、Writeともに常にマスターになります。

次回の記事へのリンク

参考文献

Xilinx社のリファレンス・マニュアルを参考にしました。

https://japan.xilinx.com/support/documentation/ip_documentation/axi_vdma/v6_3/pg020_axi_vdma.pdf

https://www.xilinx.com/support/documentation/ip_documentation/axi_videoip/v1_0/ug934_axi_videoIP.pdf