エラー発生環境と状況

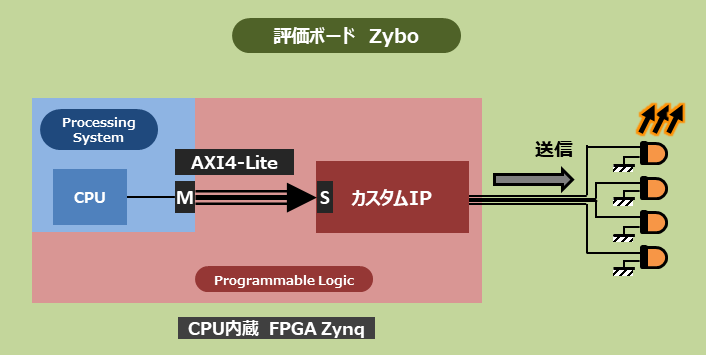

カスタムIPを含むXSAファイルから、Vitis(バージョン2020.2, 2021.1)でプラットフォームプロジェクトを生成・ビルドしたところ、makefileにおけるエラーが発生。エラーの修正方法について紹介する。

エラー発生環境

- 開発用PC: Windows 10, 64bit

- Vivado Design Suite – HLx Edition – 2020.2, 2021.1

- Vitis コア開発キット – 2020.2, 2021.1

- 開発用基板: Zybo Zynq-7010評価ボード(Board Rev.4)

- Zynq XC7Z010-1CLG400C

- カスタムIPの作成方法:以下の記事参照

エラー発生状況

以下の記事では、VivadoでカスタムIPを作成後、Vitisでプラットフォームプロジェクトを作成し、アプリケーションプロジェクトのビルドを行いました。

このとき、「プラットフォームプロジェクトのビルド時」「アプリケーションプロジェクトのビルド時」の2箇所でエラーが発生しました。

以下では、エラー発生時の状況を詳述します。

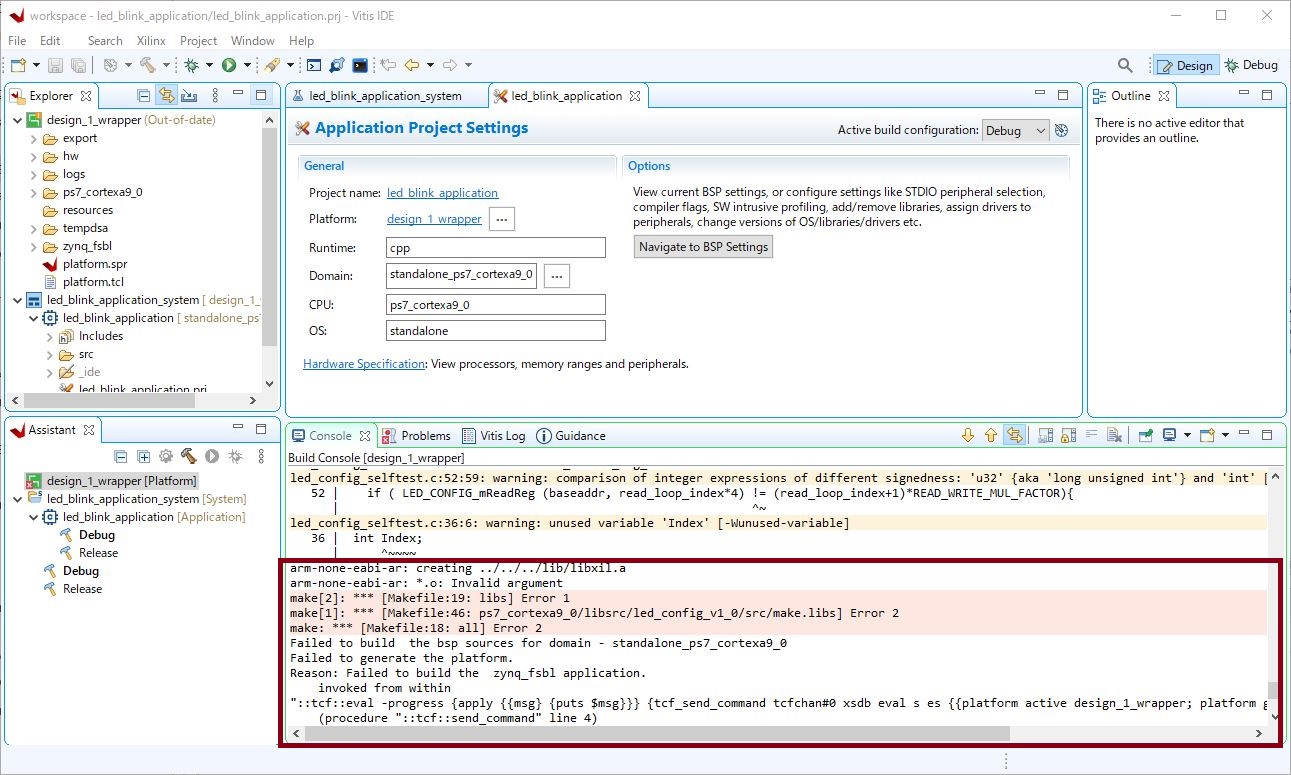

エラー発生時の状況① プラットフォームプロジェクトのビルド時

カスタムIPを含むプラットフォームプロジェクトをビルドするときに、エラーが発生しました。

XSAファイルを読み込みプロジェクトを立ち上げた直後、Assistantウィンドウのdesign_1_wrapperをビルドすると、以下のエラーが発生しました。

エラー発生時ウィンドウ

エラー発生時コンソール

arm-none-eabi-ar: creating ../../../lib/libxil.a

arm-none-eabi-ar: *.o: Invalid argument

make[2]: *** [Makefile:19: libs] Error 1

make[1]: *** [Makefile:46: ps7_cortexa9_0/libsrc/led_config_v1_0/src/make.libs] Error 2

make: *** [Makefile:18: all] Error 2

make: Leaving directory '../workspace/design_1_wrapper/zynq_fsbl/zynq_fsbl_bsp'

/*略*/

c:/xilinx/vitis/2020.2/gnu/aarch32/nt/gcc-arm-none-eabi/x86_64-oesdk-mingw32/usr/bin/arm-xilinx-eabi/../../libexec/arm-xilinx-eabi/gcc/arm-xilinx-eabi/9.2.0/real-ld.exe: cannot find -lrsa

collect2.exe: error: ld returned 1 exit status

make: *** [Makefile:27: fsbl.elf] Error 1

Building the BSP Library for domain - standalone_ps7_cortexa9_0 on processor ps7_cortexa9_0

make --no-print-directory seq_libs

/*略*/

arm-none-eabi-ar: creating ../../../lib/libxil.a

arm-none-eabi-ar: *.o: Invalid argument

make[2]: *** [Makefile:19: libs] Error 1

make[1]: *** [Makefile:46: ps7_cortexa9_0/libsrc/led_config_v1_0/src/make.libs] Error 2

make: *** [Makefile:18: all] Error 2

Failed to build the bsp sources for domain - standalone_ps7_cortexa9_0

Failed to generate the platform.エラー発生時の状況② アプリケーションプロジェクトのビルド時

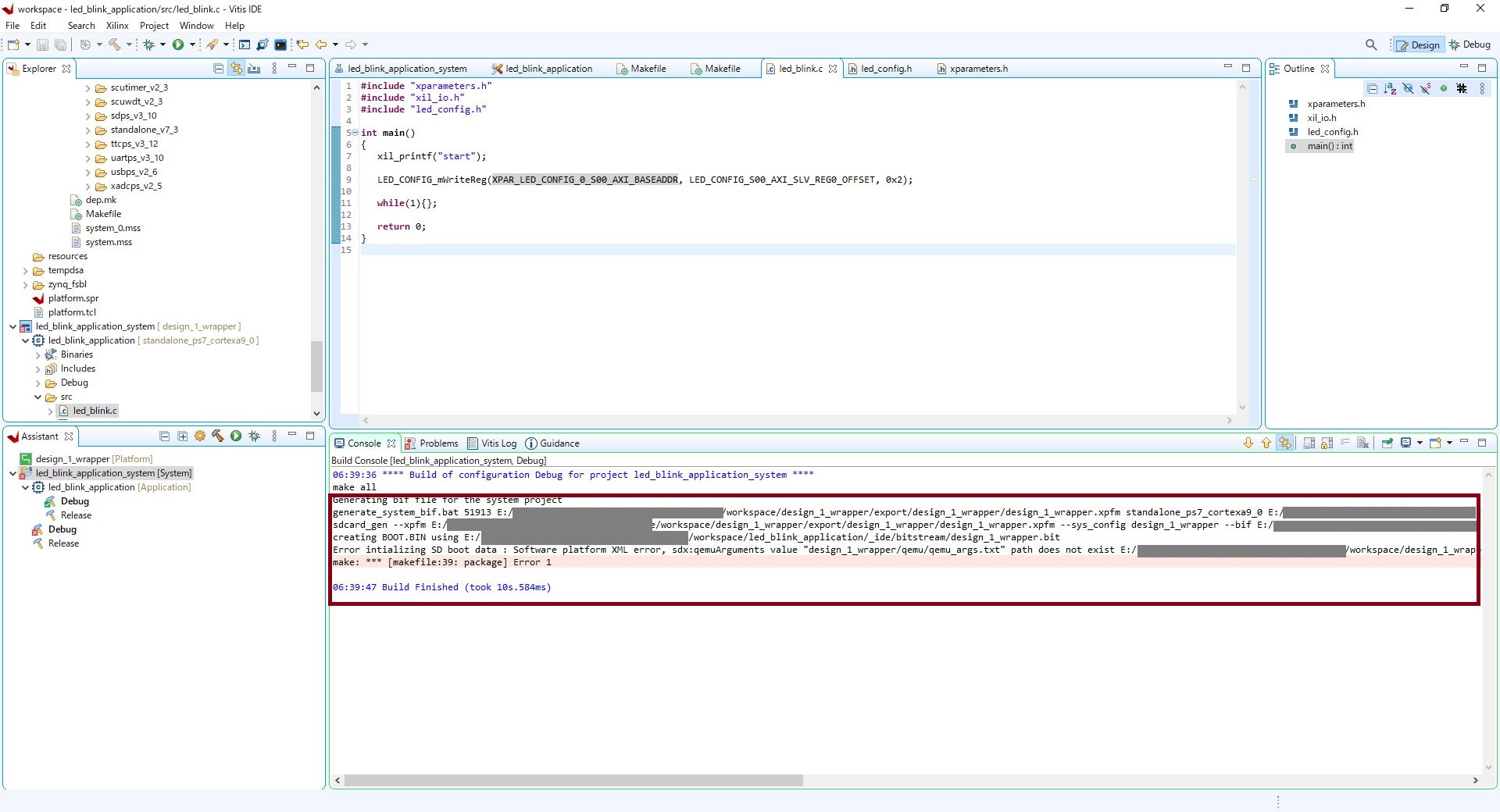

後述する対処法①によって①のビルドエラーを回避した。しかし、その後、プラットフォームプロジェクト上で動作するアプリケーションプロジェクトをビルドするときに、別のエラーが発生しました。

エラー発生時ウィンドウ

エラー発生時コンソール

Generating bif file for the system project

generate_system_bif.bat 53820 ../workspace5/design_1_wrapper/export/design_1_wrapper/design_1_wrapper.xpfm standalone_ps7_cortexa9_0 ../workspace5/design5_system/Debug/system.bif

sdcard_gen --xpfm ../workspace5/design_1_wrapper/export/design_1_wrapper/design_1_wrapper.xpfm --sys_config design_1_wrapper --bif ../workspace5/design5_system/Debug/system.bif --bitstream E:/2021-06-06/xilinxPrj/blog/10_axi4_lite/workspace5/design5/_ide/bitstream/design_1_wrapper.bit --elf ../workspace5/design5/Debug/design5.elf,ps7_cortexa9_0

creating BOOT.BIN using ../workspace5/design5/_ide/bitstream/design_1_wrapper.bit

Error intializing SD boot data : Software platform XML error, sdx:qemuArguments value "design_1_wrapper/qemu/qemu_args.txt" path does not exist ../workspace5/design_1_wrapper/export/design_1_wrapper/sw/design_1_wrapper/qemu/qemu_args.txt, platform path ../workspace5/design_1_wrapper/export/design_1_wrapper, sdx:configuration design_1_wrapper, sdx:image standard

make: *** [makefile:39: package] Error 1エラーの原因と回避方法

原因

原因について調べたところ、どうやら以下の記事で記載されている、makefileにおけるmake環境のバージョンの差異が原因のようです。

再現環境について調査できておりませんが、Windows版Vitis 2020.2のバージョンがあまり良くないようです。今後のVitisのアップデートで修正されることを願っています。

エラーを回避してビルドを行う対処法

対処法① プラットフォームプロジェクトのビルド時

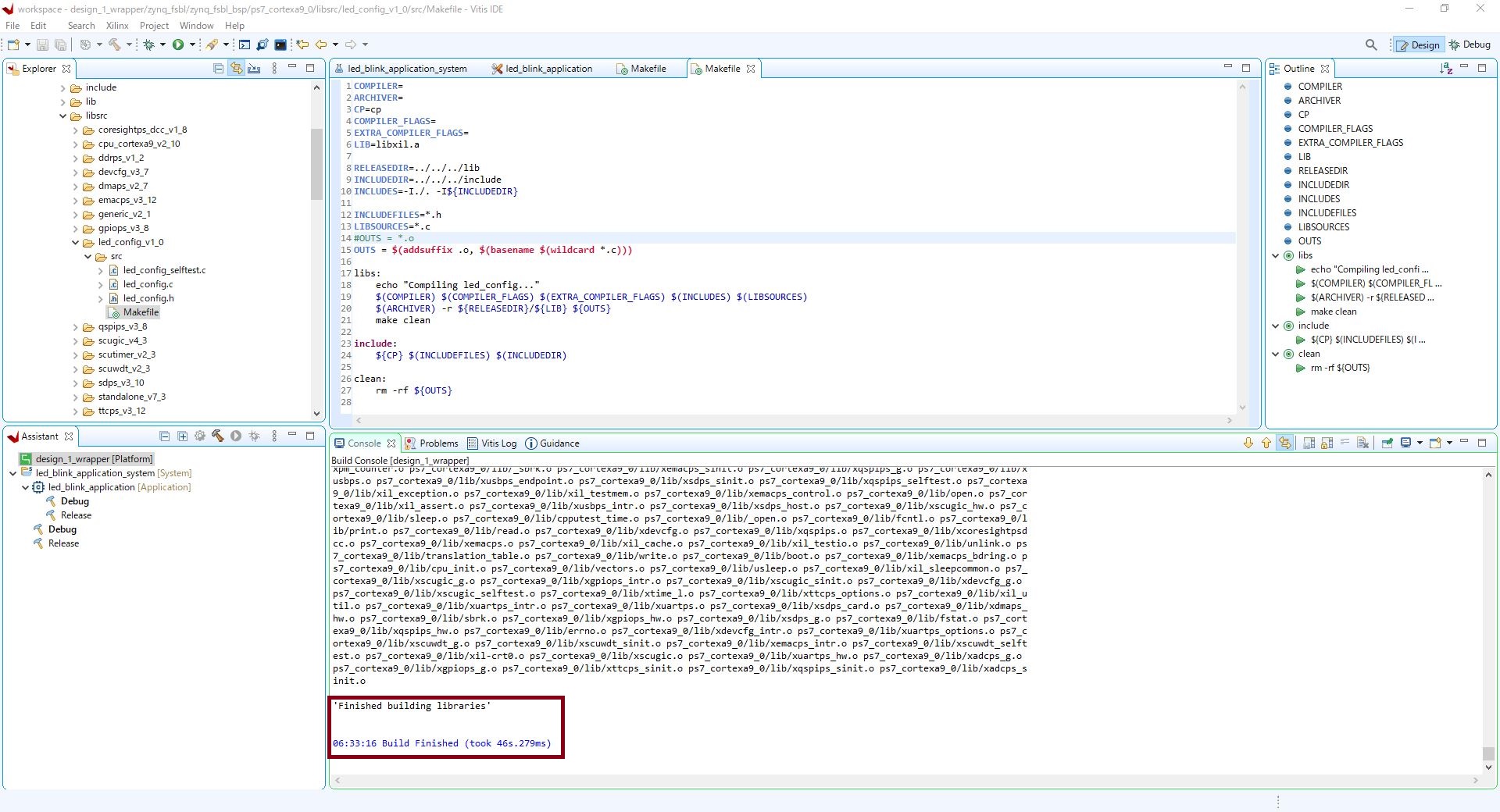

上述した記事の内容に従い、makefileを以下のように修正しました。

修正が必要だったmakefileは、Vitis IDEの左のExplorerに含まれる、以下のパスに入っている2つのファイルです。

- design_1_wrapper

- ps7_cortexa9_0

- standalone_ps7_cortexa9_0

- bsp

- [ps7_cortexa9_0>libsrc>led_config_v1_0>Makefile]

- bsp

- standalone_ps7_cortexa9_0

- zynq_fsbl

- zynq_fsbl_bsp

- [ps7_cortexa9_0>libsrc>led_config_v1_0>Makefile]

- zynq_fsbl_bsp

- ps7_cortexa9_0

bspフォルダとzynq_fsbl_bspフォルダ内にある、カスタムIPのMakefileを修正しました。

カスタムIPが多いときは手におえませんが、今回は2つだけですので、地道に修正を行いました。

修正方法は、以下のようにMakefileにおける[OUTSの定義文]を変更しました。

#OUTS = *.o

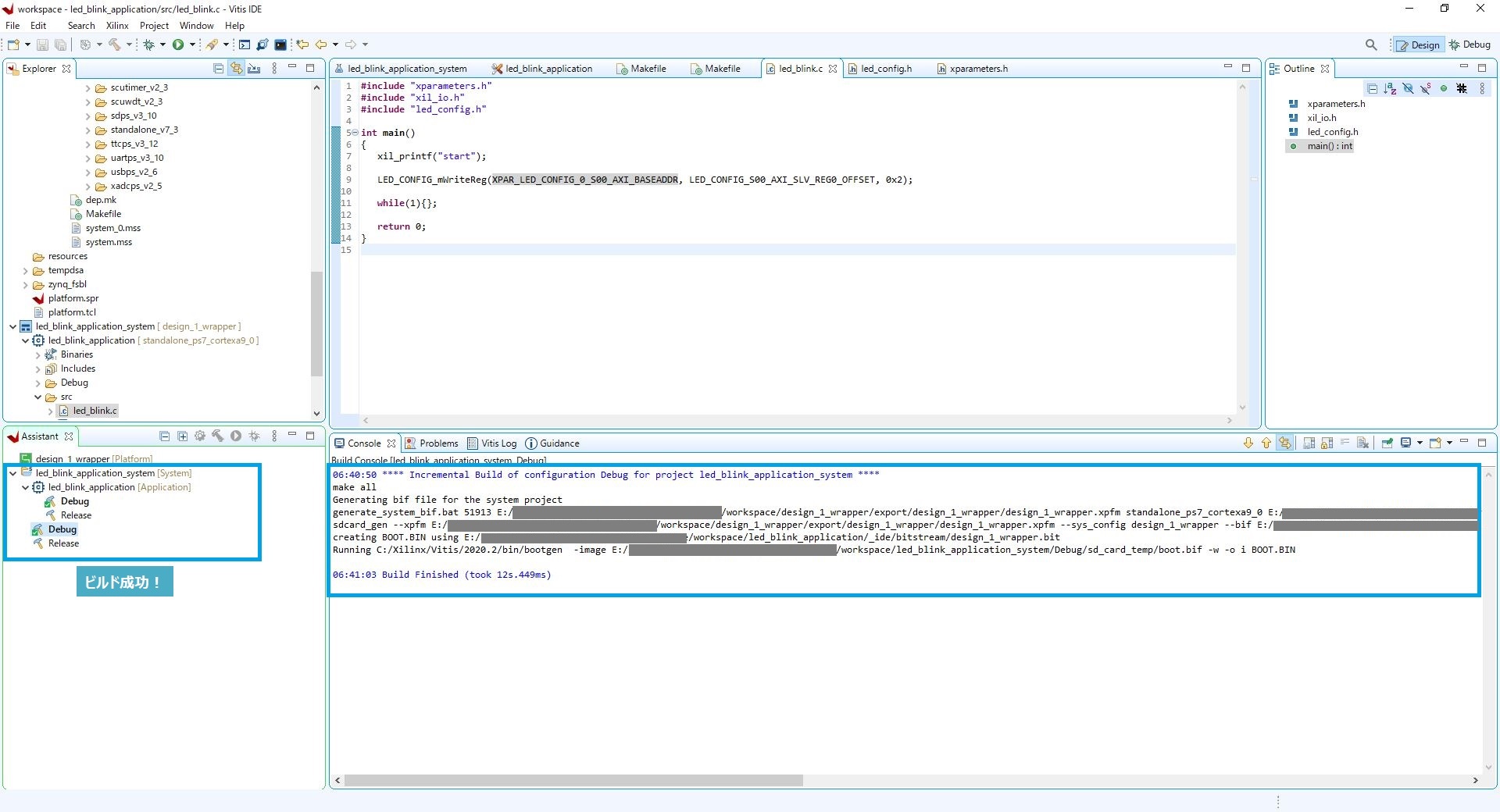

OUTS = $(addsuffix .o, $(basename $(wildcard *.c)))Makefileを修正すれば、以下のようにプラットフォームプロジェクトのビルドが通るようになります。

対処法② アプリケーションプロジェクトのビルド時

以下のDigilentのフォーラムでは、”you have just to re-export hardware after making the changes in the makefile and rebuild.(makefile変更後にハードウェアを再度エクスポートし、再ビルドしないといけない)”との報告があります。

そこで、以下のようにしてXSAファイルのアップデートを行いました。

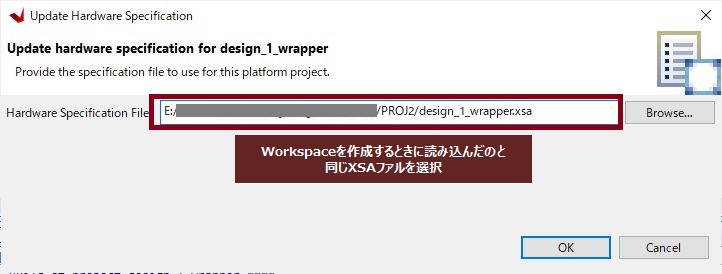

プラットフォームプロジェクトを右クリックし、[Update Hardware Specification]を選択します。

新しいウィンドウが立ち上がります。ここで、workspaceを作成するときに読み込んだものと同じXSAファイルを選択します。

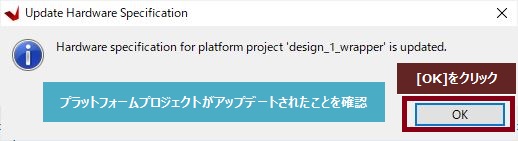

OKをクリックし暫く待つと、プラットフォームプロジェクトがアップデートされたことを示すウィンドウが立ち上がるので、確認したら[OK]をクリックします。

このアップデートを行うと、無事にアプリケーションプロジェクトの方もビルドが通るようになります。

本記事では、カスタムIPを含むプラットフォームプロジェクトで発生したmakefileのエラーの回避方法を解説しました。

少し手間がかかる方法なのでよりよい方法が見つかったり、最新のVitisのアップデートでエラーが回避されていた場合は、改めて追記します。

最後までご覧いただきありがとうございました。

2021/7/17の追記

結論は、Vitis2021.1のアップデートでは、上述した「カスタムIPにおけるMakefileの不具合」は、まだ解消されていないようです。

また、エラー発生状況①でのエラーコードが異なりました。

対処法①も、前回やった方法ではうまく行かず、Twitterで教えていただいた別の方法でうまくいきました。

本サイトでは、Vitis2021.1での状況と対処法をそれぞれ追記しておきます。

Vitis2021.1でのMakefileエラー発生状況

カスタムIPをVivado ML 2021.1で作成。ブロックデザインは、以下の記事シリーズで記載したものと同じ構成を再現。

エラー発生状況①

カスタムIPを含むプラットフォームプロジェクトをビルドするときにエラーが発生。

エラー発生時ウィンドウ

エラー発生時コンソール(エラー部分を抜粋)

arm-xilinx-eabi-gcc.exe: error: *.c: Invalid argument

arm-xilinx-eabi-gcc.exe: fatal error: no input files

compilation terminated.

make[3]: *** [Makefile:18: libs] Error 1

make[2]: *** [Makefile:46: ps7_cortexa9_0/libsrc/myip_v1_0/src/make.libs] Error 2

make[1]: *** [Makefile:18: all] Error 2

make[1]: Leaving directory '.../workspace/design_1_wrapper/zynq_fsbl/zynq_fsbl_bsp'

make: *** [Makefile:30: zynq_fsbl_bsp/ps7_cortexa9_0/lib/libxil.a] Error 2

Building the BSP Library for domain - standalone_ps7_cortexa9_0 on processor ps7_cortexa9_0

make --no-print-directory seq_libs

/*略*/

arm-xilinx-eabi-gcc.exe: error: *.c: Invalid argument

arm-xilinx-eabi-gcc.exe: fatal error: no input files

compilation terminated.

make[2]: *** [Makefile:18: libs] Error 1

make[1]: *** [Makefile:46: ps7_cortexa9_0/libsrc/myip_v1_0/src/make.libs] Error 2

make: *** [Makefile:18: all] Error 2

Failed to build the bsp sources for domain - standalone_ps7_cortexa9_0

Failed to generate the platform.

/*略*/Vitis2021.1でのエラーの回避方法

対処法① プラットフォームプロジェクトのビルド時

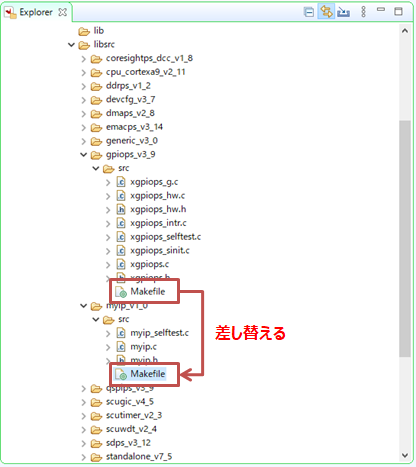

makefileを以下のように修正しました。

修正が必要だったmakefileは、Vitis IDEの左のExplorerに含まれる、以下のパスに入っている2つのファイルです。

- design_1_wrapper

- ps7_cortexa9_0

- standalone_ps7_cortexa9_0

- bsp

- [ps7_cortexa9_0>libsrc>led_config_v1_0>Makefile]

- bsp

- standalone_ps7_cortexa9_0

- zynq_fsbl

- zynq_fsbl_bsp

- [ps7_cortexa9_0>libsrc>led_config_v1_0>Makefile]

- zynq_fsbl_bsp

- ps7_cortexa9_0

修正方法は、カスタムIPのMakefileを、カスタムIPではないXilinx提供のIP(例えば、GPIO)のlibsrcフォルダの中にあるMakefileで差し替えます。

Makefileを修正すれば、プラットフォームプロジェクトのビルドが通るようになります。

コメント