こんにちは。FPGAプログラミング初学者の「ひがし研究所」です!

企業のエンジニアとして働きつつ、FPGAを使ったデジタル回路の設計に興味を持ち、休日に勉強をしています。

初学者の目線から、詰まりやすいポイントとそれを解決した方法について、記事にしていこうと思いますので、ぜひご覧いただければと思います!

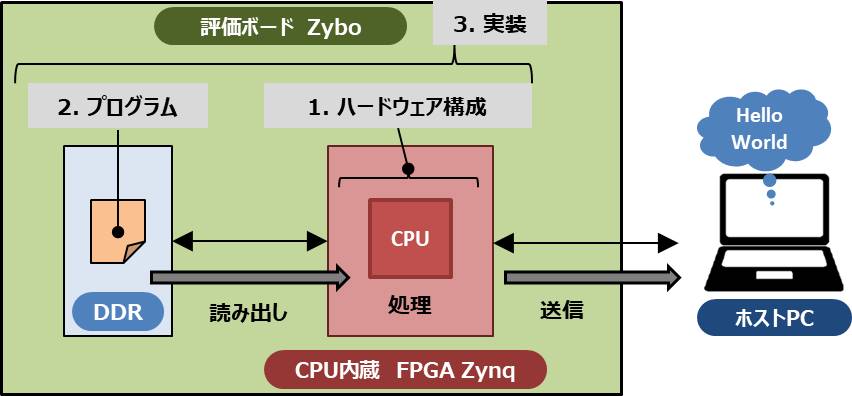

では、今回の記事では、CPUとFPGAのプログマブルロジックが搭載された、Xilinx社のZynqを初めて扱う人が、最初に作る”Hello World”のプログラムを実行する方法についてまとめます。

- FPGAプログラミングの初学者

- Zynqを用いた設計は未経験のエンジニア

- FPGAの開発に興味のある学生

それでは、興味のある方はぜひ最後までご覧ください!

1. 目標と工程

開発目標

本記事では、次の記事と2回に分けて、

Zynq CPUで処理した”Hello World”プログラムからの出力をホストPCで受信する

これを目標とします。

開発工程

① FPGA内部のハードウェア構成を定めるプロジェクトを作成

② Zynq CPUで動作する”Hello World”プログラムを作成

③ ①と②を実装

本記事は長くなりましたので、開発ボードZyboとシステムの構成を説明した後、開発工程のうち①までを行います。

次回の記事で残りの仕上げに取り掛かります。

今回、以下の書籍を参考にさせていただきました。

2. システムの構成

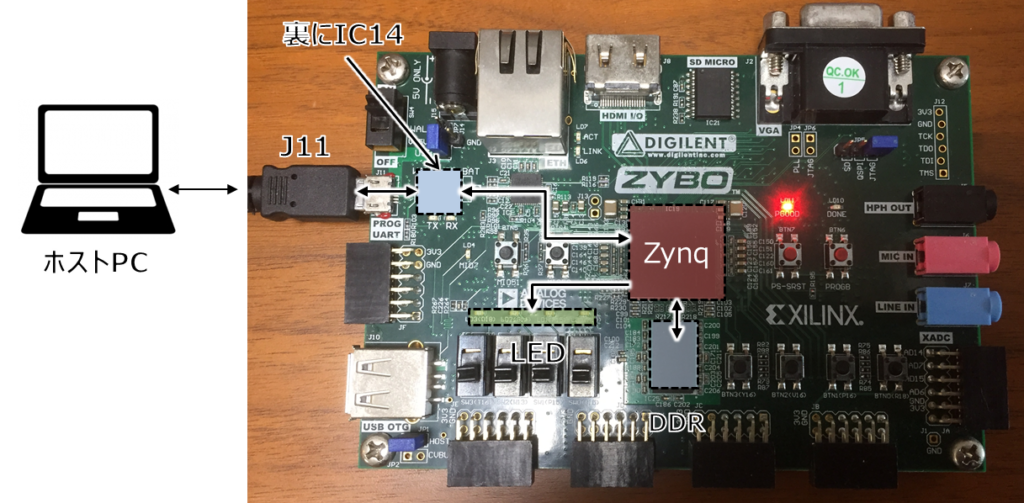

開発ボード Zybo Zynq-7010評価ボード

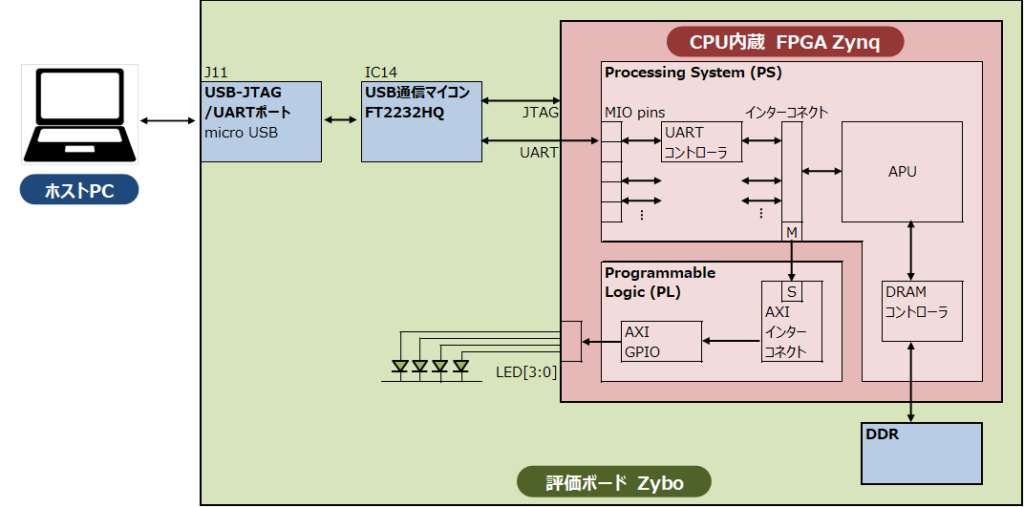

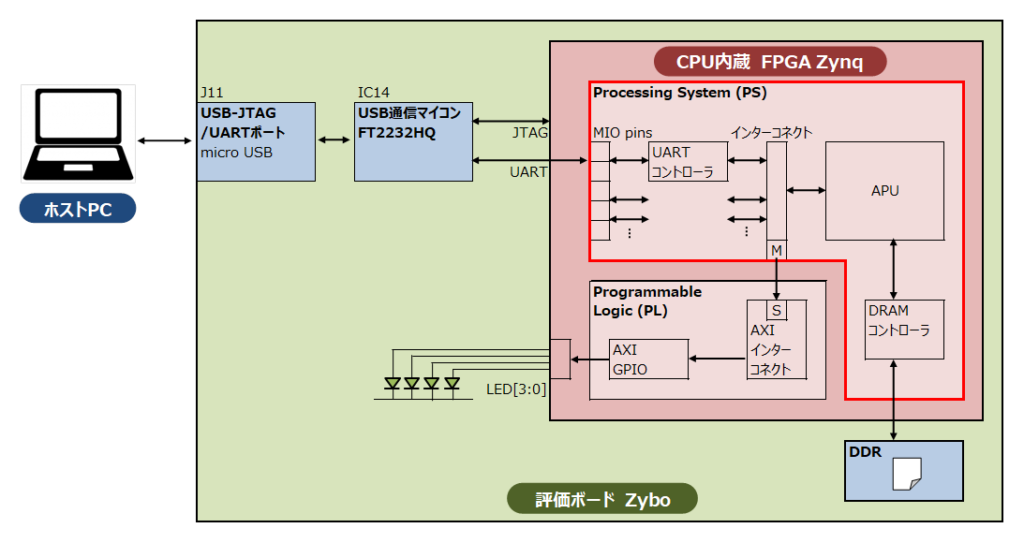

Zyboのシステム構成図

Zyboのマニュアルを参考にまとめると、以下のようなシステム構成になります。

※本記事で必要なところのみを抜粋しています。実際の回路基板には他にも多くの有用な機能が含まれます。

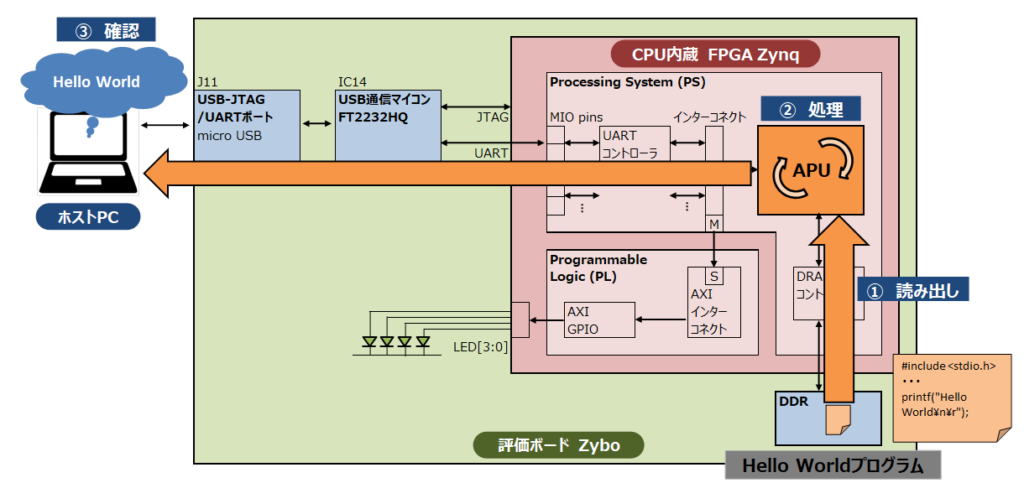

動作原理

動作原理のポイントは以下の通りです。

① DDRメモリから”Hello World”プログラムを読み込む

② CPUで処理

③ 処理結果をホストPCで確認

動作させるために、必要なプロジェクトとプログラムを設計していきます。

Xilinx FPGA向けの開発ツール”Vivado Design Suite”(通称、Vivado)でロジックを設計し、

ホストPCからJTAG経由で、PL (Programmable Logic ;Zynq上で回路を構築するFPGA部分)に設計したロジックを書き込みます。

PS(Processing System;CPUに加え、イーサネットやUSB、DDRメモリと通信するための周辺回路も内蔵されたブロック)とホストPCは、シリアルポートのUARTを介して交信します。

”Hello World”の文字列は、UARTを経由してPS内のAPU(Application Processor Unit;デュアルコアのCPU+α)からシリアル通信でホストPCに送信されます。

受信した文字列は、ホストPCで確認しましょう。

DDRメモリには、CPUを動かすためのプログラムが格納されています。

今後、LED点滅も試してみるので、ブロック図にはLED出力端子も記載しましたが、本日のテーマではこのモジュールは必要ありません。

3. プロジェクトの作成

準備作業(Zyboのボードの読み込み)

新しいプロジェクトを作成する前に、Zyboのボードに関するファイルを読み込んでおく必要があります。

ボードファイルの読み込み方法は、この記事を参照してください。

ハードウェア設計(CPUと周辺回路の構成)

プロジェクトを作成し、”Create Block Design”をクリックし真っ白な作業スペースのブロックデザインを立ち上げます。

ブロックデザイン上で”Add IP”をクリックし、”ZYNQ7 Processing System”を選択しましょう。そうするとブロックダイアグラム上にモジュールが一つだけ配置されます。

”Run Block Automation”をクリックし、今回のボード Zyboに対応したPSの設定を読み込みます。

※Zyboのボードに関するファイルを読み込んでおかないとここで詰まりますので注意!

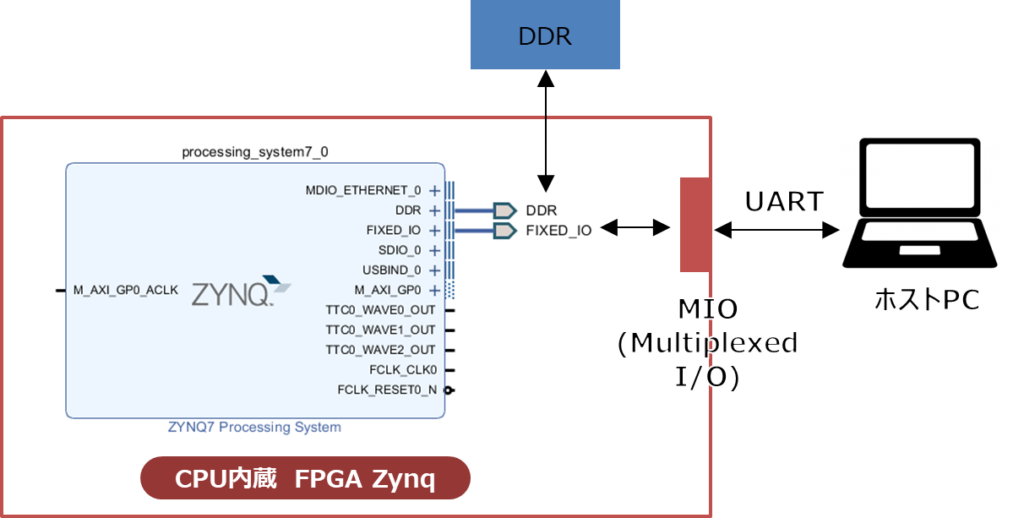

既に、”DDR”と”FIXED_IO”とタグ付けされたポートが接続されています。

このポートを介してそれぞれボード上のDDRメモリと、イーサネットやUSBのような周辺回路との、信号の入出力を行います。

DDR … Zybo上のDDRメモリとの信号の入出力

FIXED_IO … イーサネットやUSBのような周辺回路との信号の入出力

FIXED_IOにおける周辺回路との接続を行うインターフェースは、MIO(Multiplexed I/O)と呼ばれています。

このMIOのうち、今回はホストPCに”Hello World”の文字列を送信するためのUARTのポートのみを使用します。

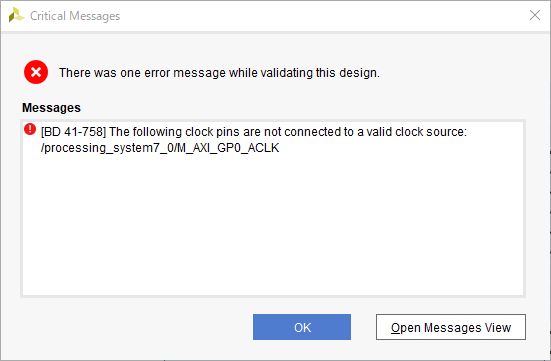

このブロックだけで、”Hello World”のプログラムを実行するのに十分なモジュールは揃っているのですが、このままダイアグラムをもとにHDLファイルを作ろうとするとエラーが発生します。

これはPL側との接続を行うAXI ポート”GP0″のクロック(M-AXI_GP0_ACLK)に何も接続されていないためです。

今回のテーマでは、PL側にロジックを組む必要はないので、AXI ポート”GP0″は使用しません。

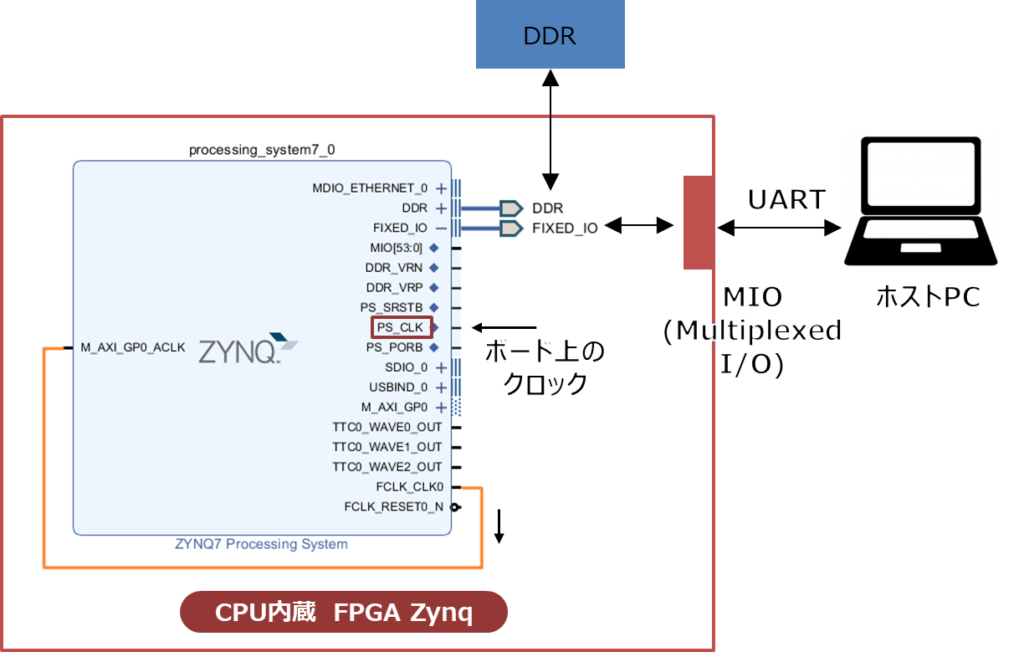

そこで、このクロックも当然使用しませんが、エラー回避のため、図のように”FCLK_CLK_0”から”M-AXI_GP0_ACLK”へのクロック出力を繋ぐことで対処します。

ちなみに、”FCLK_CLK_0”はPLにクロックを提供する目的でPS側から出力されています。PSにおけるクロックはボード上に搭載されている振動子50MHzをもとに生成され、そのクロックがCPUやDDR、内蔵周辺回路、そしてそれを分周したものをPL側に提供しているようです。

極めてシンプルな、ブロックダイアグラムが作成されました。

これを”Generate Bitstream”でコンパイルしていきます。

この作業までで、図の赤枠のPSのハードウェアの構築までが完了しました。

あとは、ソフトウェア側の構築、つまりCPUを動かすためのプログラムを作成するだけです!

まとめ:システムの構成とハードウェアプロジェクトの設計

以上をまとめると、この通り。

“Hello World”プログラムをFPGAに実装するためのシステム構成をVivadoプロジェクトで設計

- プログラムを実行するためのCPUが搭載されたFPGA Zynq

- プログラムを格納するためのDDRメモリとの入出力ポート

- 信号を送信するホストPCとのUART出力ポート

本日の記事を踏まえて、次回、いよいよ”Hello World”プログラムの作成と実装を行います!

コメント