Vitis

Vitis 【外部映像送受信(3)】Zynq上で外部映像を送受信するアプリケーション(受信系の作成① HDMI接続時の割り込みハンドラの構成)

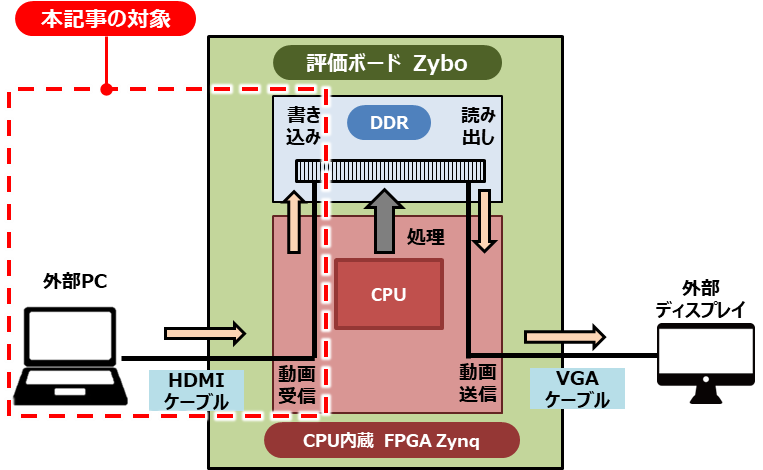

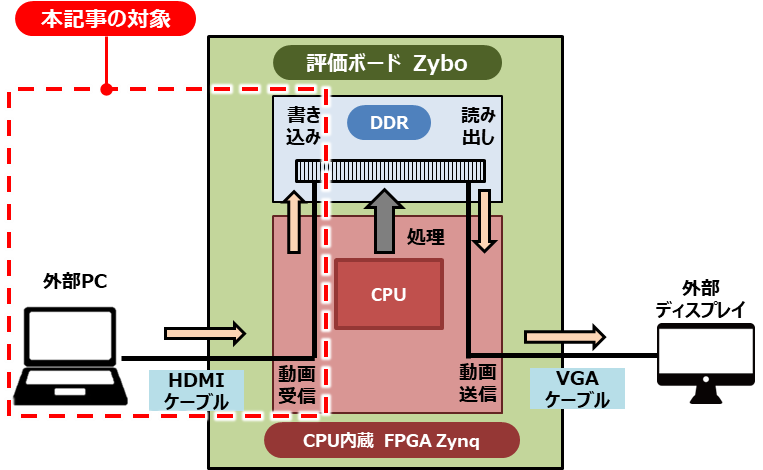

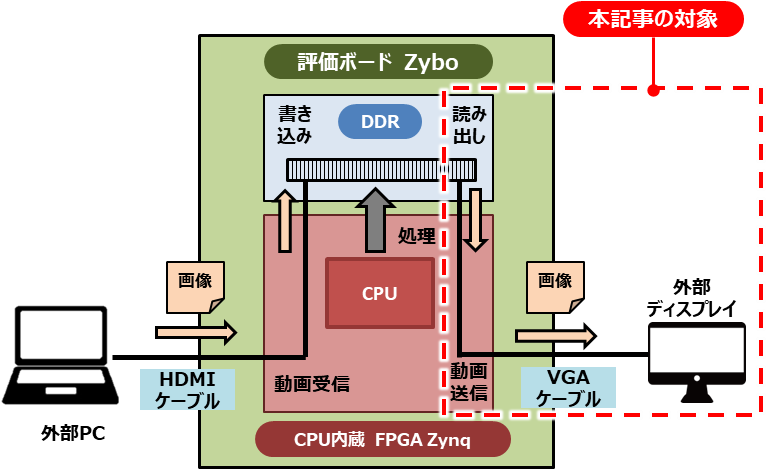

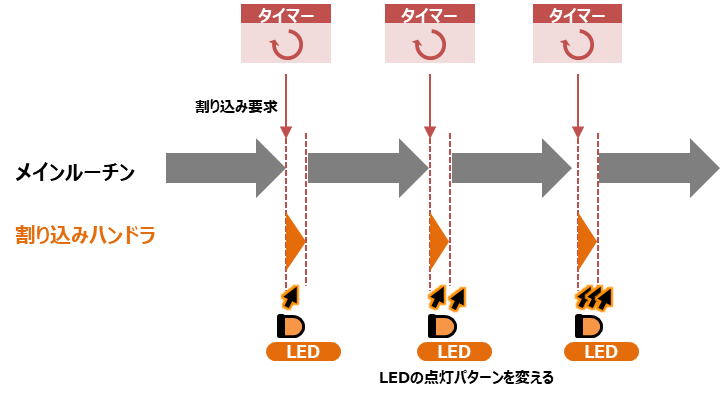

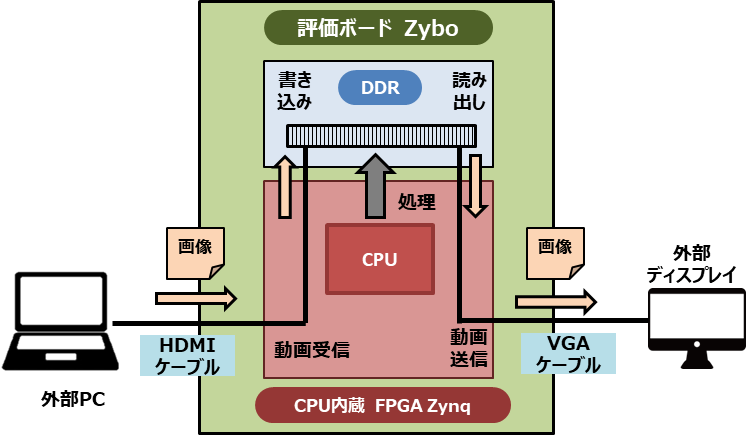

FPGA Zynqが外部からのHDMI信号を受信しDDRメモリに格納した後、DDRメモリを読み出しVGA信号を送信するアプリケーションの解説を行っています。HDMI信号をZynqが受信する際の割り込みの設定方法について紹介・解説しました。

Vitis

Vitis  Vitis

Vitis  Vitis

Vitis  Vitis

Vitis  Vitis

Vitis  Xilinx SoC

Xilinx SoC  Xilinx SoC

Xilinx SoC  Xilinx SoC

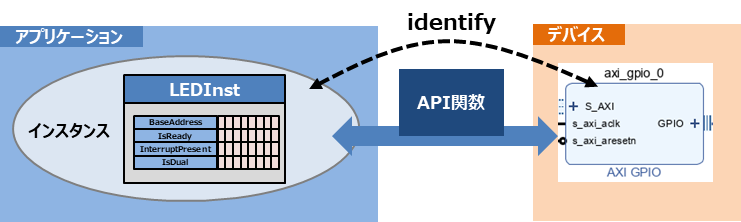

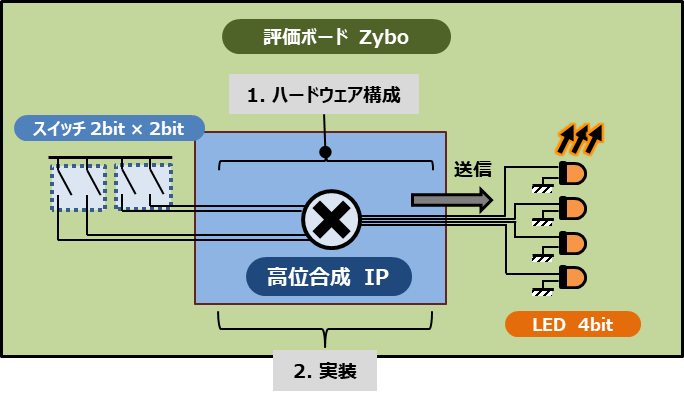

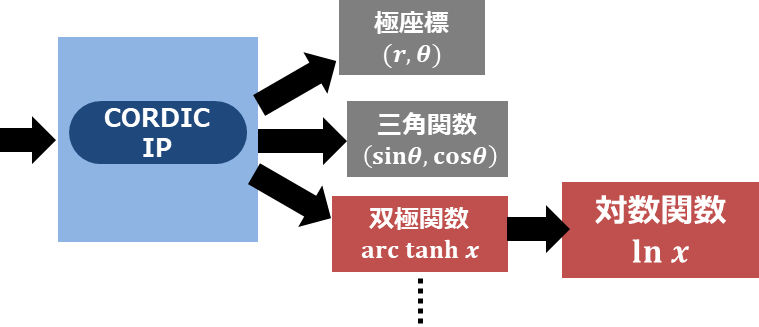

Xilinx SoC  IP

IP