本記事の概要

“LED点滅”プログラムをFPGAに実装するためためのブロックデザインをVivado 2020.2上で作成。ブロックデザイン上で以下のIPを配置し、制約ファイルの作成を行った。

- LEDへの信号を出力するために新しくAXI GPIOを追加

- 自動でAXIインターコネクト、リセット信号出力のIPを追加し、配線

これまでFPGAを用いたシステム開発には、ハードウェア設計にVivado、ソフトウェアアプリケーションの開発にXilinx SDKを用いられてきました。

しかし、2019年以降、ソフトウェアアプリケーションの開発は、Xilinx SDKから統合ソフトウェア開発環境「Vitis」へと移行しています。

「Vitis」での開発環境に慣れ親しんでおくためにも、前回の記事で作成した”Hello World”アプリケーションを応用し”LED点滅”アプリケーションを、Vitis 2020.2で作成しました。

今回の記事では、統合ソフトウェア開発環境VitisとXilinx FPGA向け設計ツール Vivadoを用いて、開発ボードZybo (搭載SoCチップ Zynq)に実装する”LED点滅”アプリケーションを作成する方法についてまとめます。

- FPGAプログラミングの初学者

- FPGAの開発に興味のある学生

- Vitisを用いたアプリケーション開発は未経験のエンジニア

それでは、興味のある方はぜひご覧ください!

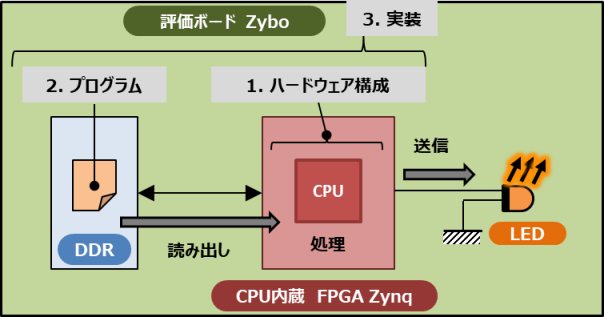

1. 目標と工程

開発目標

本記事の目標は次の通りです:

統合ソフトウェア開発環境VitisとFPGA設計環境Vivadoを用いて

Zybo上の”LED”を点滅させるアプリケーションを作成する

開発工程

① FPGA内部のハードウェア構成を定めるプロジェクトを作成(本記事)

② Zynq CPUで動作する”LED点滅”プログラムを作成

③ ①と②を実装

2. システムの構成

開発環境

- 開発用PC: Windows 10, 64bit

- Vivado Design Suite – HLx Edition – 2020.2

- Vitis コア開発キット – 2020.2

- 開発用基板: Zybo Zynq-7010評価ボード(Board Rev.4)

- Zynq XC7Z010-1CLG400C

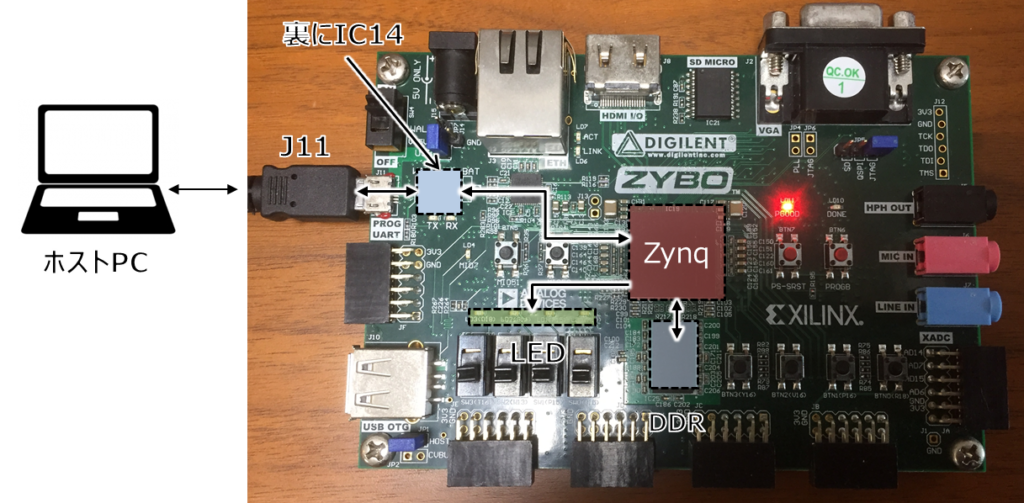

開発ボード Zybo Zynq-7010評価ボード

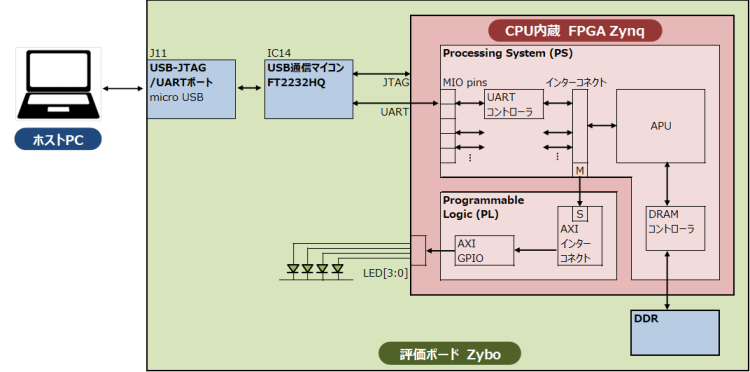

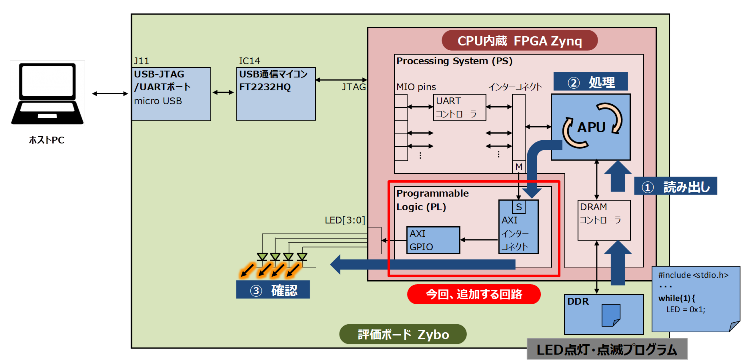

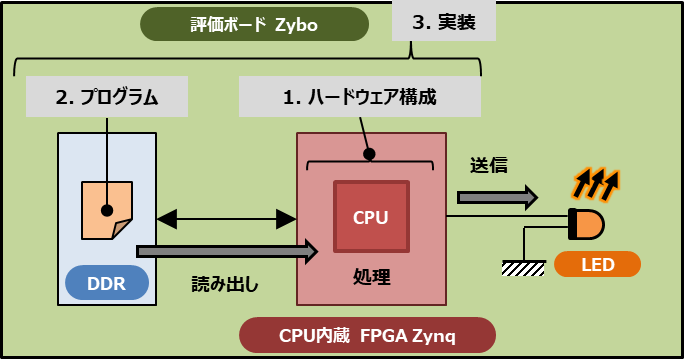

Zyboのシステム構成図

Zyboのマニュアルを参考にまとめると、以下のようなシステム構成になります。

※本記事で必要なところのみを抜粋しています。実際の回路基板には他にも多くの有用な機能が含まれます。

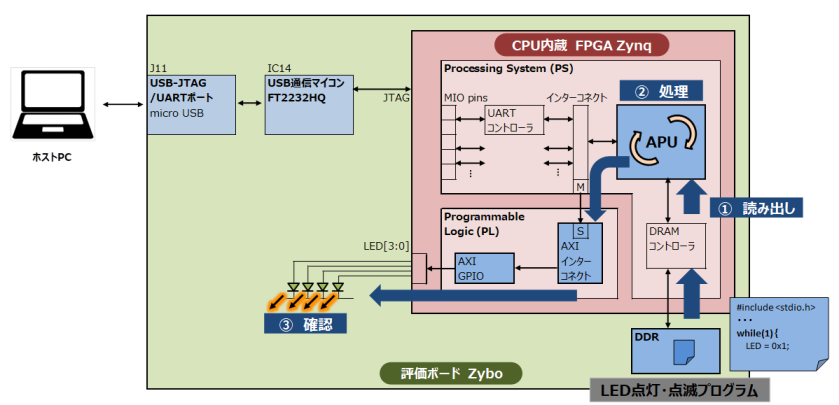

動作原理

動作原理のポイントは以下の通りです。

① DDRメモリから”LED点灯・点滅”プログラムを読み込む

② CPUで処理

③ LEDを点灯・確認

Xilinx FPGA向けの開発ツール”Vivado Design Suite”(通称、Vivado)でロジックを設計し、ホストPCからJTAG経由で、PL (Programmable Logic)に書き込みます。

PS(Processing System)では”LED点灯・点滅プログラム”を処理・実行し、

LEDを制御する信号(電圧がHighなら点灯、Lowなら消灯)をインターコネクト、GPIO(General-purpose input/output;汎用入出力)を介して、LEDの端子に出力します。

インターコネクトは、LED出力やVGA出力、マイク入力などの種々の入出力を交通整理して、CPUと交信するためのハブの役割を果たしています。

ちなみに、このとき用いる通信規格(プロトコル)は、AXIバスと呼ばれるものを用いており、Xilinx社のIPの多くがAXIバスでの入出力が可能になっています。

3. プロジェクトの作成

準備作業(Zyboのボードの読み込み)

新しいプロジェクトを作成する前に、Zyboのボードに関するファイルを読み込んでおく必要があります。

ボードファイルの読み込み方法は、この記事を参照してください。

ハードウェア設計(CPUと周辺回路の構成)

Vivado 2020.2のプロジェクトの作成

前回の記事では”Hello World”アプリケーションを動作させるためにVivadoプロジェクトを作成しました。このVivadoプロジェクトを変更することによって、新しく”LED”点滅回路用のプロジェクトを設計していきます。

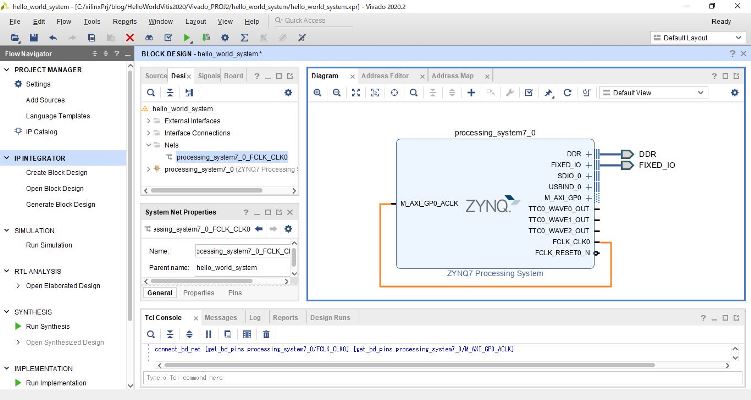

ブロックデザインの作成

“Hello World”アプリケーションには、すでにシステム構成図のPS(Processing System)を表すIPが追加されています。

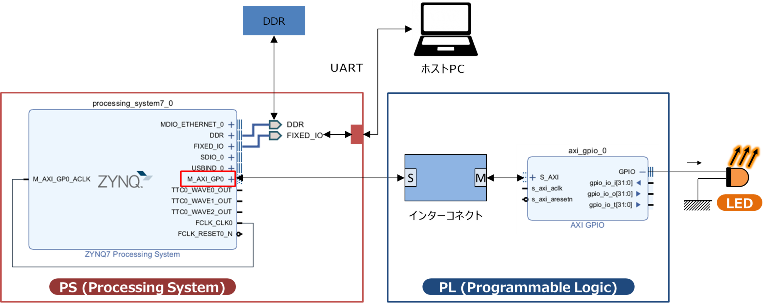

今回の”LED点滅”アプリケーションには、システム構成図で赤線で囲っている、[AXI GPIO]と[AXIインターコネクト]が必要です。

ブロックデザインでは、まずこの2つのIP([AXI GPIO]と[AXIインターコネクト])を追加し、IP間を結線していきます。

設計の概念図は、このようになります。

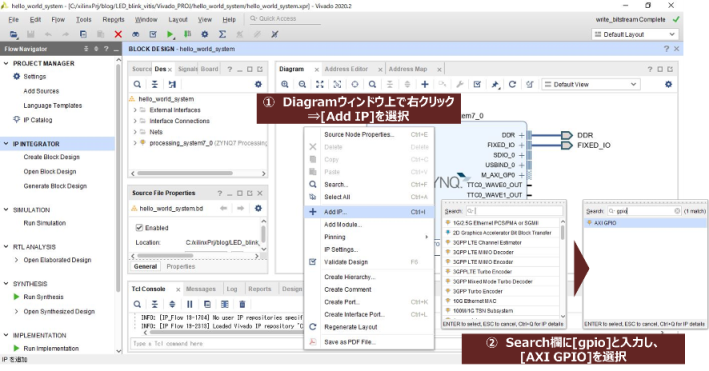

前回作成した、”Hello World”アプリケーションのブロックデザインを開きます。

ブロックデザインの余白内で右クリックをし、[Add IP]を選択します。

新しくウィンドウが立ち上がりますので、追加したい[AXI GPIO]を表すIPを探します。

そこで、Search欄に“gpio”と入力し、[AXI GPIO]を選択します。

そうすると、ブロックダイアグラムにIP axi_gpio_0が追加されます。

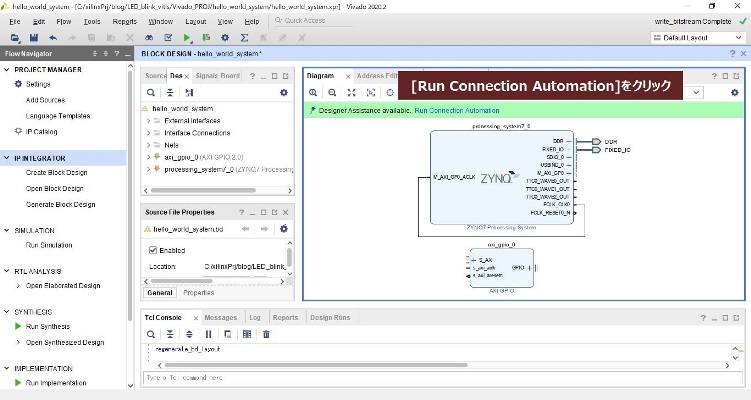

次に、追加するのは[AXIインターコネクト]を表すIPですが、このIPは[Run Connect Automation]をクリックすれば自動で追加・結線されます。

[Run Connect Automation]をクリックしてみましょう。

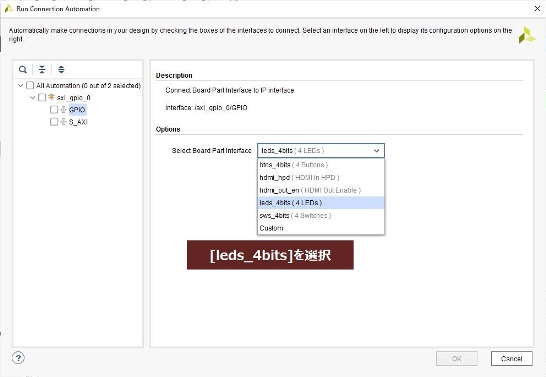

新しくウィンドウが立ち上がります。このウィンドウでは、追加したIP axi_gpio_0と他のIPやI/O(外部入出力端子)とを接続するかを指定します。

まず、IP axi_gpio_0の送信先を指定します。

本記事の目的は、Zynq上で処理したCプログラムに基づいて、Zybo上のLEDを点滅させることでしたので、出力先にLEDを選択します。ウィンドウ上では[led_4bits (4 LEDs)]を選択します。

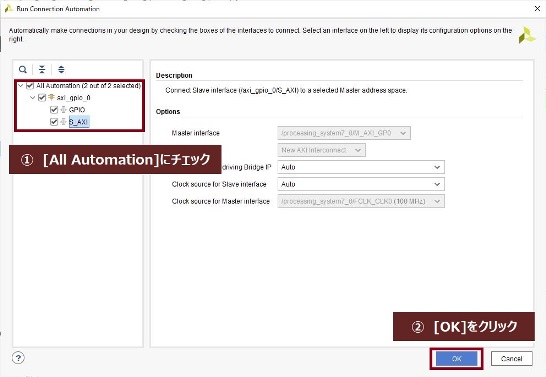

次に、IP axi_gpio_0の受信元を選択する必要がありますが、ブロックダイアグラム上には受信元になりうるIPがZynq Processing Systemを表すIP(processing_system7_0)しかありませんので、特に指定はしなくても自動で結線されます。

図にように、[All Automation]にチェックを入れて、[OK]をクリックし、IP間の結線を行います。

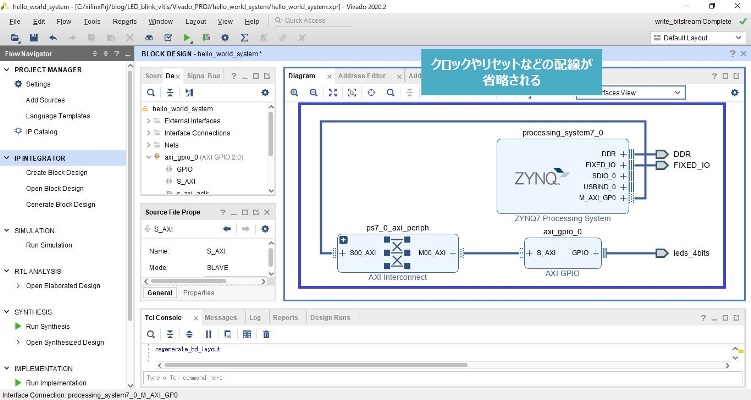

このように、IPが追加され、自動でIP間が接続されます。

AXIインターコネクトを表すIP ps7_0_periphと、IPに応じて適切なリセット信号を接続先の各IPに提供するIP [Processor System Reset]も追加されています。

前回の”Hello World”アプリケーションに比べると、多少、複雑なブロックデザインが生成されました。

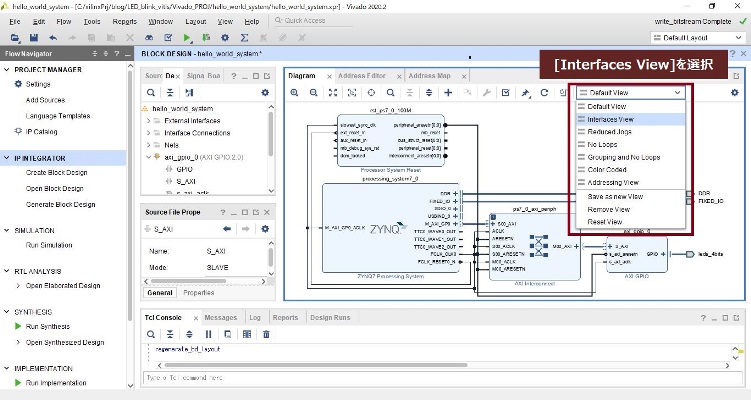

ちなみに、モジュールの可読性を悪くしている原因は、リセットやクロックの配線が複雑なためです。

ブロックダイアグラムの右上にあるダイアグラムの表示モードを選択するリストから[Interface View]を選択すれば、よりシンプルで、可読性が良い表示に切り替えることが可能です。

この図のように、Processing Systemからインターコネクトを介して、LEDに信号を出力する、目的の回路設計ができました。

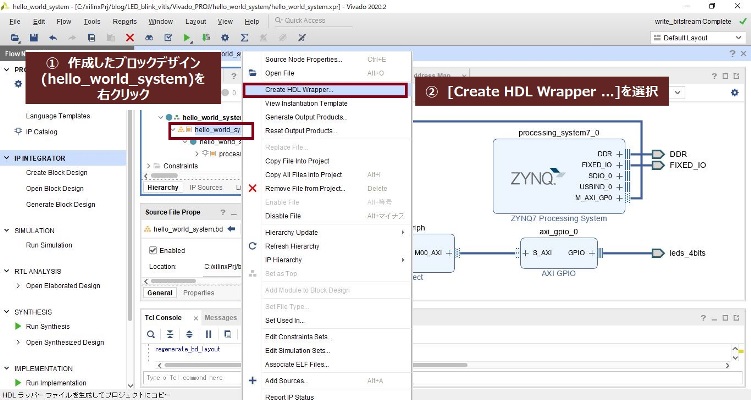

最後に、ブロックデザインの設計が完了したら、設計をもとにHDL(ハードウェア言語)を作成しておきましょう。

作成したブロックデザインのデザイン名[hello_world_sytem]を右クリックし、[Create HDL Wrapper …]を選択します。

長くなりましたが、これでブロックデザインの作成は完了です。

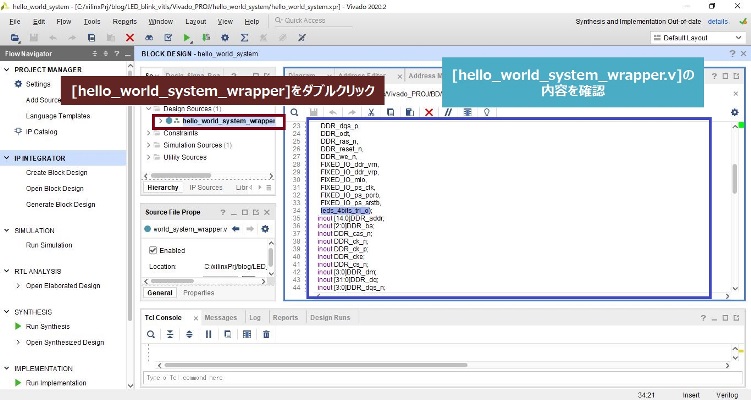

制約ファイルの作成

次に、LEDへの出力信号がFPGAのどのピンから出力されるか、制約ファイル上で定義します。

作成されたHDL(hello_world_sytem_wrapper.v)をダブルクリックして、LEDへの出力を表す変数名を確認します。

変数名は[led_4bits_tri_o]という名前であることがわかります。

確認できたら、制約ファイルの作成に移ります。

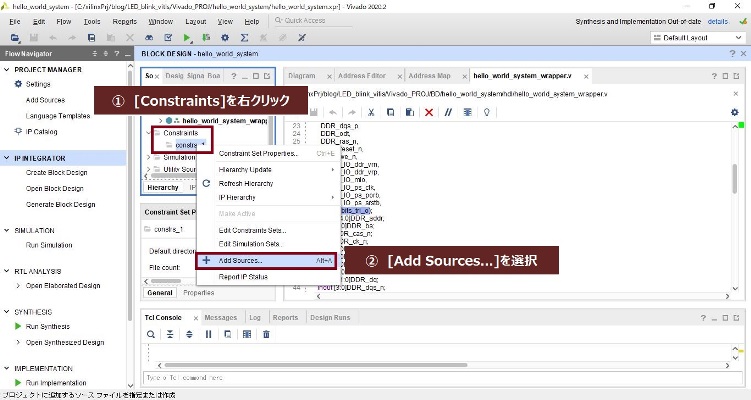

[Source]欄の[Constraints]フォルダを右クリックし、[Add Sources…]を選択します。

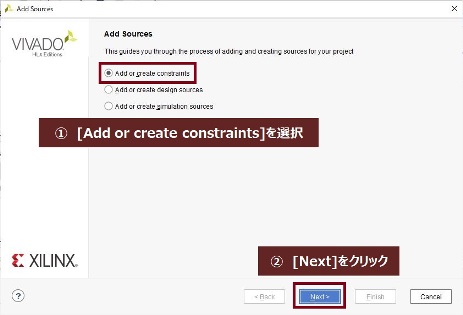

作成するファイルの種類を、以下の3種類から選択します。

- 制約ファイル (constraints)

- 設計ファイル (design sources)

- シミュレーションファイル (simulation sources)

今回は、制約ファイルの作成ですので、[Add or create constraints]を選択し、[Next]をクリックします。

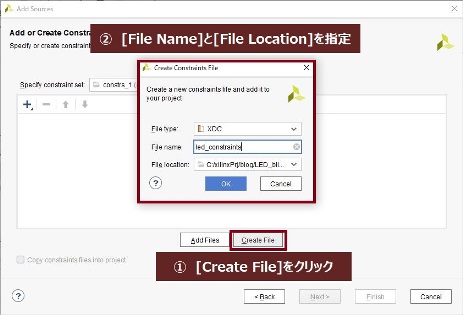

「既にある制約ファイルを追加する」と「新しく制約ファイルを作る」の、いずれかを選択できます。

今回は「新しく制約ファイルを作る」ので、[Create File]をクリックします。[ファイルの名前]と[ファイルの格納先]をそれぞれ選択したら、[OK]と[Finish]をクリックします。

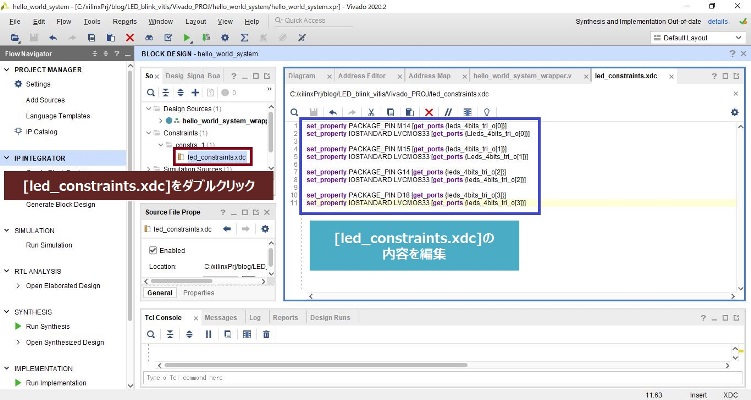

作成された[led_constraints.xdc]をダブルクリックし、制約ファイルを編集していきます。

コードは以下の通りです。

set_property PACKAGE_PIN M14 [get_ports {leds_4bits_tri_o[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {Lleds_4bits_tri_o[0]}]

set_property PACKAGE_PIN M15 [get_ports {leds_4bits_tri_o[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {Leds_4bits_tri_o[1]}]

set_property PACKAGE_PIN G14 [get_ports {leds_4bits_tri_o[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds_4bits_tri_o[2]}]

set_property PACKAGE_PIN D18 [get_ports {leds_4bits_tri_o[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds_4bits_tri_o[3]}]“leds_4bits_tri_o”という変数にそれぞれFPGA上のピンを割り当てています。

FPGAのピンの配置(M14,M15,G14,D18など) は以下のリンク先の”13 Basic I/O”で確認できます。

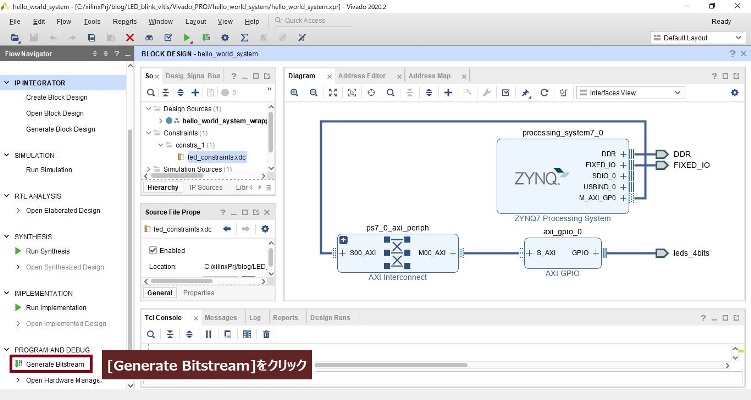

論理合成、配置配線、bitstreamファイルの作成

この制約ファイルのもとで、[Generate Bitstream]で論理合成、配置配線、bitstreamファイルの作成までを一気に行っていきます。

この作業までで、ハードウェアの構築までが完了しました。

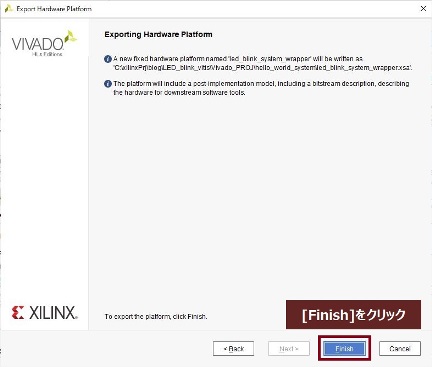

ハードウェアデザインのエクスポート (XSAファイルの作成)

構築したハードウェア設計をXSAファイルにエクスポートして、次回作成するアプリケーションプロジェクトの準備をしておきましょう。

基本的に、”Hello World”プログラムの場合と同じです。

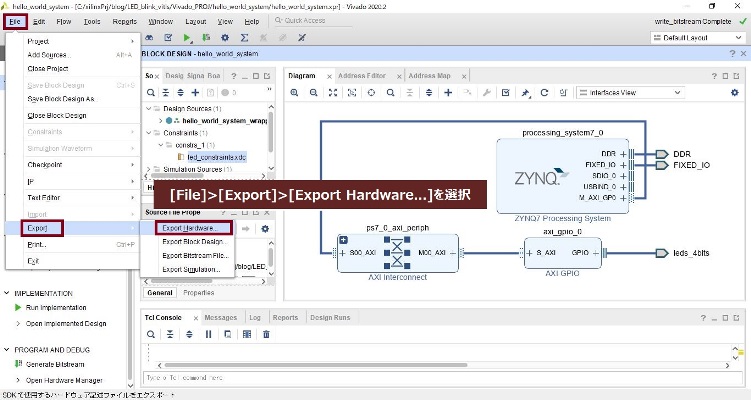

まず、[File]から[Export]>[Export Hardware…]を選択します。

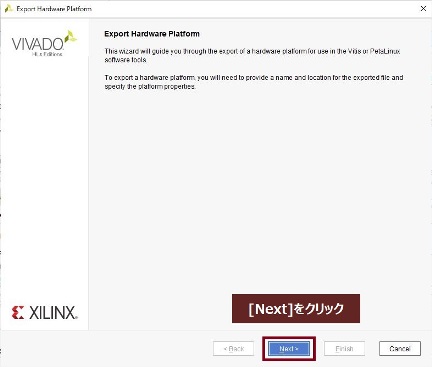

立ち上がった新しいウィンドウ上で、エクスポートの設定を確認していきます。

まず、[Next]をクリックします。

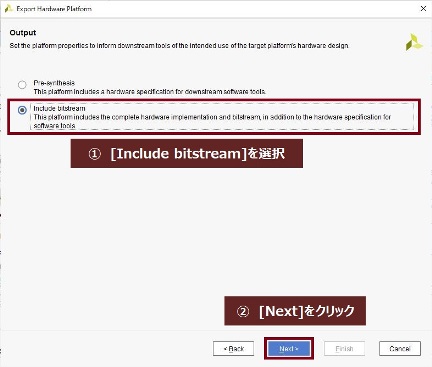

[Include bitstream]を選択し、[Next]をクリックします。

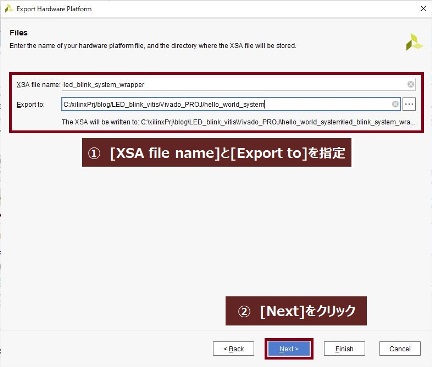

ファイル名とエクスポート先を指定し、[Next]をクリックします。

最後に、[Finish]をクリックして完了です。

お疲れさまです。あとは、ソフトウェア側のプログラム設計だけです。

長くなりましたので、今回はハードウェアの構築までとします。

次回は実際にLEDが点滅する様子を確認したいと思います!

コメント