本記事の概要

Digilent社では、Zybo用のデモサンプル「Zybo HDMI Input Demo」が提供されています。

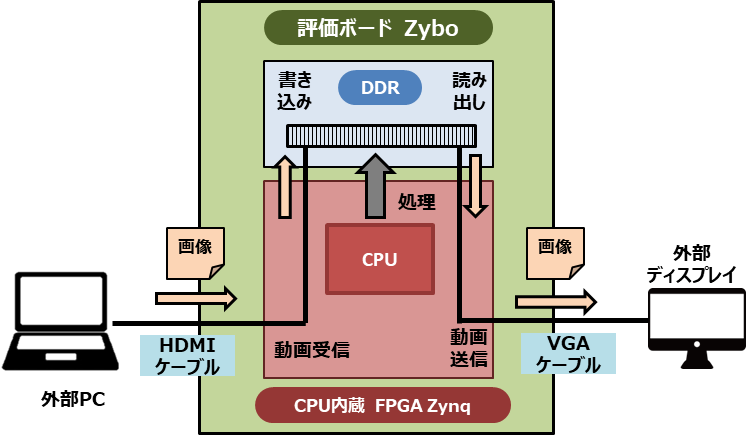

デモサンプルの内容は、「外部からのHDMI信号をZynqが受信しDDRメモリに格納。その後、DDRメモリを読み出しVGA信号を送信する」というものです。

本記事では、デモサンプルをVivadoで読み込み、ハードウェアデザインを作成しました。以下の内容についてまとめました:

- デモサンプルで提供されるブロックデザインの構成と動作原理

- AXI VDMAの設定の修正(Data Realignment Engine(DRE)の設定が必要)

- bitファイルを含むXSAファイルの出力までの具体的な実行方法

Vitisでは、画像処理アプリケーションを開発する上で有用なライブラリ(Vitis ビジョンライブラリ)が豊富に用意されています。

Vitisビジョンライブラリを試していくことを視野に入れ、筆者はZynqの画像送受信に関係するIPの使い方について勉強しています。

これまで、既存のデモサンプルを活用しながら、関連するIPについてまとめました。

例えば、Digilent社の「Zybo HDMI Output Demo」を試して、Zyboから外部ディスプレイへ静止画を出力することができるようになりました。

デモサンプルを通じ、以下のXilinxのビデオ送受信に有用なIPコアの理解を深めることができるので、一度デモサンプルを試してみるのをおすすめします。

- AXI VDMA (Video Timing Controller)

- Video Timing Controller

今回の記事では、外部から受信した動画像の映像信号をZynqで受信し、それを外部に出力する、別のデモサンプルを試してみました。

前回のデモサンプルに、さらに外部からの信号を受信するモジュールやドライバを追加しており、構成や原理を理解する難易度が少しだけ上がります。

しかし、徐々にステップアップするという意味で、このデモサンプルはよい教材になると思います。

- FPGAの開発に興味のある学生

- Vitisを用いたアプリケーション開発は未経験のエンジニア

- FPGAでの動画像処理を行いたいエンジニア

それでは、興味のある方はぜひ最後までご覧ください!

目標と工程

開発目標

本記事の目標は次の通りです:

統合ソフトウェア開発環境VitisとFPGA設計環境Vivadoを用いて

Zybo上で「HDMI信号を受信しDDRメモリに保存し、それを外部ディスプレイに出力する」

Digilent社のデモアプリケーションを作成する

開発工程

① DigilentのHPからHDMI入力デモのサンプルプログラムをダウンロード(本記事)

② デモサンプルからZynq SoC内部のハードウェア構成を定めるプロジェクトを読み込む(本記事)

③ デモサンプルからZynq SoCのARM CPUで動作する”HDMI出力”プログラムを読み込む

④ ①と②を実装し、動作確認

システムの構成

開発環境

- 開発用PC: Windows 10, 64bit

- Vivado Design Suite – HLx Edition – 2020.2

- Vitis コア開発キット – 2020.2

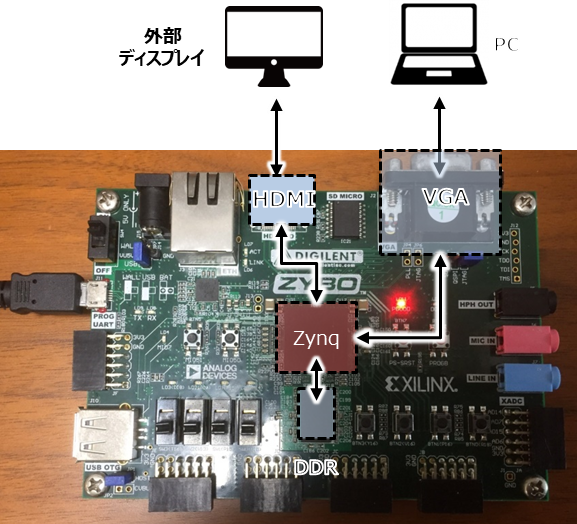

- 開発用基板: Zybo Zynq-7010評価ボード(Board Rev.4)

- Zynq XC7Z010-1CLG400C

開発ボード Zybo Zynq-7010評価ボード

動作原理

動作原理のポイントは以下の通りです。

Zynqの構成

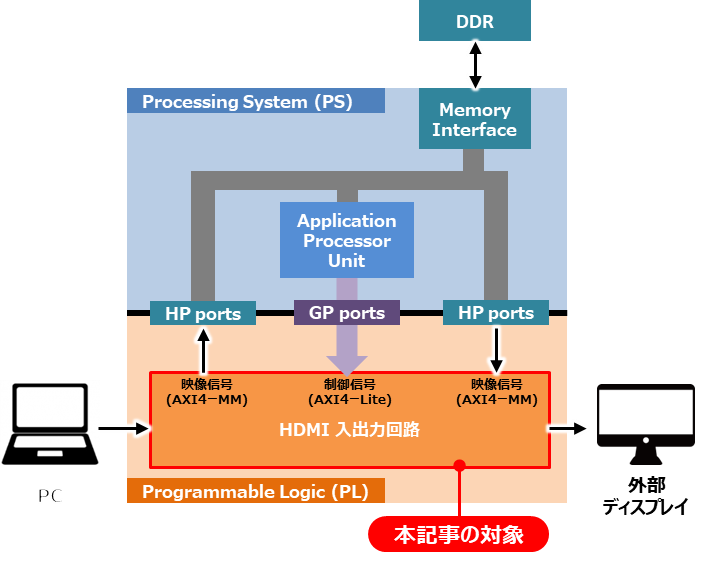

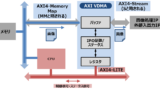

上の図のように、Zynqの内部構成を模式化してみました。

Zynqは外部から映像信号を受信し、PL(Programmable Logic)部からHigh-Performance Ports(HPポート)を通じてDDRメモリに映像信号を書き込みます。

今回の記事では、外部信号にPCからのHDMI信号を用います。

DDRメモリに書き込まれた映像信号に対して、APU(Application Processor Unit)から加工や画像処理、あるいは機械学習などの認識処理などを行うことが可能です。

今後、APU内部のドライバ関数の理解が深まれば、いろいろと試してみたいですね。

今回は、特に画像処理は行わず、ただ単に受信したままの映像をHPポートを通じて、PL部、そしてVGA出力に変換して外部ディスプレイへと出力します。

PL部に作成したHDMI入出力回路には、各種の動画像処理に有用なIPコアが準備されていますが、このIPコアを制御する制御信号や状態を示すステータス信号は、General-Purpose Ports (GPポート)を通じてAPUへ送受信されます。

Zynq-7000 SoCのテクニカルリフェレンスより、各ポートのスループットと推奨する使用方法については以下の通りです。

| 手段 | 推奨する使い方 | スループット(Estimated) |

| PL AXI_HP DMA | 大容量のデータセットをDMA形式で伝送 | 1,200 MB/s (複数のインタフェースそれぞれ) |

| PL AXI_GP DMA | ・PLとPS間の制御信号の伝送 ・PS I/O ペリフェラルのアクセス | 600MB/s |

この比較表によると、以下のように設定するのが良いかと思います。

デモサンプルでも基本的に推奨する方法で使用されていました。

- ビデオの送受信は大容量かつ高速な伝送が求められるので、AXI4 Memory MapはHPポートに接続

- 制御信号やステータス信号をやり取りするAXI4-LITEのバスはGPポートに接続

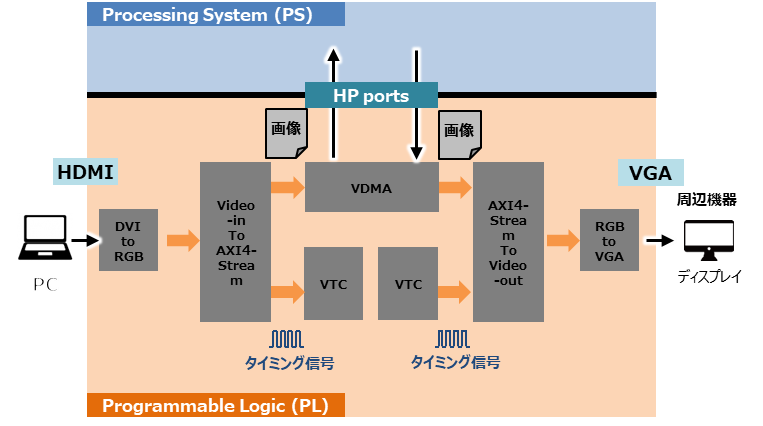

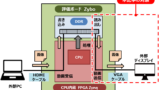

Programmable Logic (PL)部のIP構成

もう少しPL内部のIPコアの構成について、詳しく見てみましょう。

今回構成するIPは以下の通りです。

① DVI-RGB変換(dvi2rgb):HDMI(DVI)信号をRGB信号に変換

② Video-in to AXI4-Stream変換:RGB信号を映像信号を伝送するAXI4-Streamとタイミング信号に分割

③-(a) AXI Video Direct Memory Access(VDMA):周辺機器から受信した映像信号をDMA方式でDDRメモリに書き込む。逆に、DDRメモリの映像信号を読み出し、出力する。

③-(b) Video Timing Controller (VTC):タイミング信号を検出・生成する。

④ AXI4-Stream to Video Out:タイミングコントローラの信号に合わせて、入力されるAXI4-StreamのデータをRGB出力に変換。

⑤ RGB-VGA変換(rgb2vga) : 動画のRGB出力をVGA出力に変換する

処理や機能が複雑なVDMAとVTCの2つのIPコアについては、下記の記事で解説していますので、ぜひご覧いただければと思います。

以上が、動作原理に関する説明です。

では、デモサンプルを読み込んでいきましょう。

プロジェクトの作成

準備作業(HDMI出力デモサンプルのダウンロード)

まずは、HDMI入力のデモサンプルをDigilentのHPからダウンロードしていきましょう。

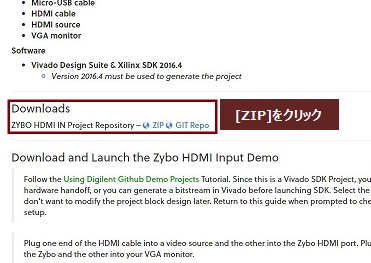

上記HPを開くと、ページの真ん中にDownloadsという項目があります。

そこの[ZIP]もしくは[GIT Repo]から、HDMI入力デモのプログラムをダウンロードします。

ダウンロードが完了したら解凍し、適当なフォルダに格納しておきます。

ハードウェア設計(CPUと周辺回路の構成)の読み込み

Vivadoのプロジェクトの作成

デモサンプルの読み込みは、Tclスクリプトというファイルを走らせることによって行います。

Vivadoでは、コマンドの入力にTcl (Tool Command Language)と呼ばれるスクリプト言語を用いています。

ブロックダイアグラムの作成や論理合成などの処理は、これまでGUI上でコマンドを選択して行っていますが、Tclスクリプトで記載されたコマンドをコンソール上に書き込むことによって動作させることも可能です。

今回、この一連のコマンドをまとめて一つのファイルにしたTclスクリプトを走らせることによって、デモサンプルの読み込みを行います。

前回の記事と重複する内容になりますので、改めて確認したい方は[+]マークから詳細をご確認ください。

Tclスクリプトの実行

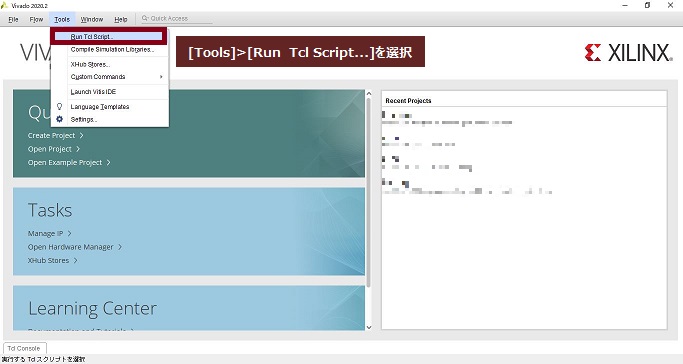

Vivadoを立ち上げ、メニューバーから[Tools]>[Run Tcl Script…]を選択

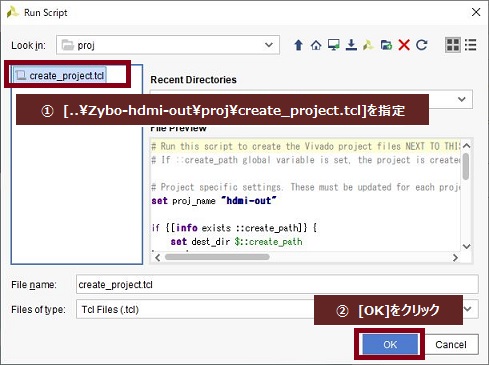

Tclファイルを選択するウィンドウが現れます。

先ほどダウンロードし解凍したデモサンプル[Zybo-hdmi-in]の中から、[proj]>[create_project.tcl]を選択し、[OK]をクリック。

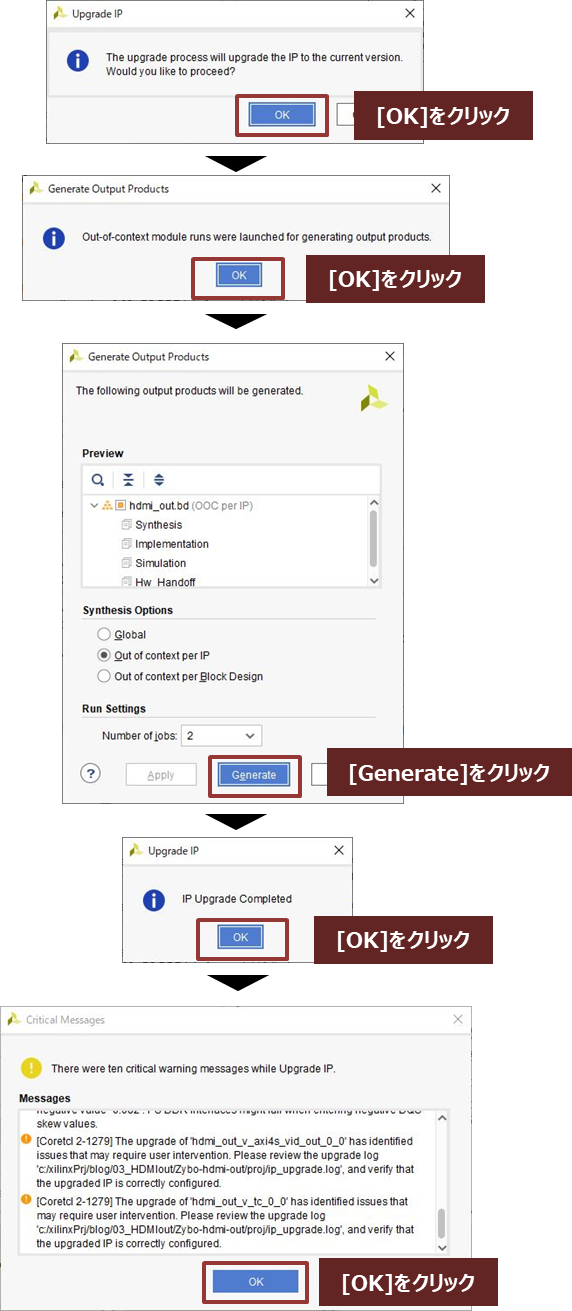

ブロックデザインの生成とIPのアップデート

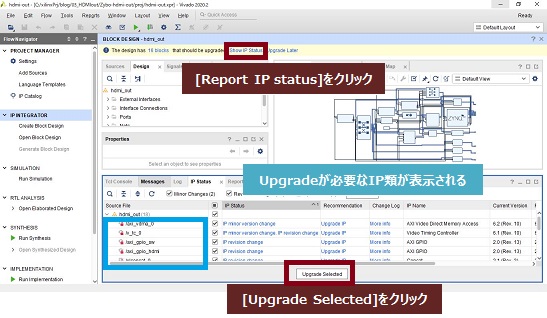

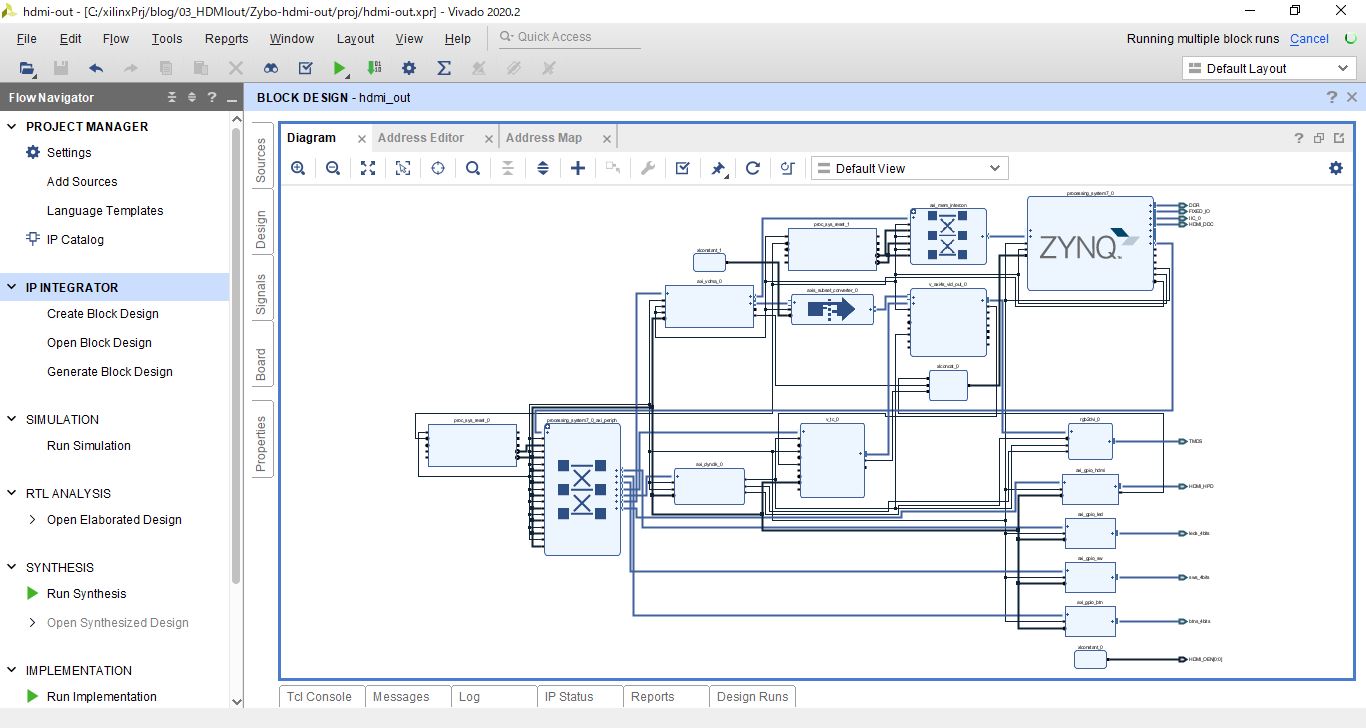

読み込みが始まり、ブロックダイアグラムが自動で生成される。

デモサンプルファイルに含まれる、Digilentが提供する有用なIP類も同時に追加される。

生成されたブロックダイアグラムには、多数のIPが配置され、配線も自動で繋がれている。

ただし、VivadoのバージョンがDigilent社の提供時と異なるため、IPのアップグレードが必要。

黄色で表示されたインフォメーションから[Report IP status]をクリック。

そうすると、アップグレードが必要なIPがIP Status上に表示されるので、[Upgrade Selected]をクリックし、これらのIPをまとめてアップグレード。

指示に従い、順に[OK]をクリックしていけば、アップグレードが完了。

一連のアップグレードが完了すると、ブロックダイアグラムが完成。

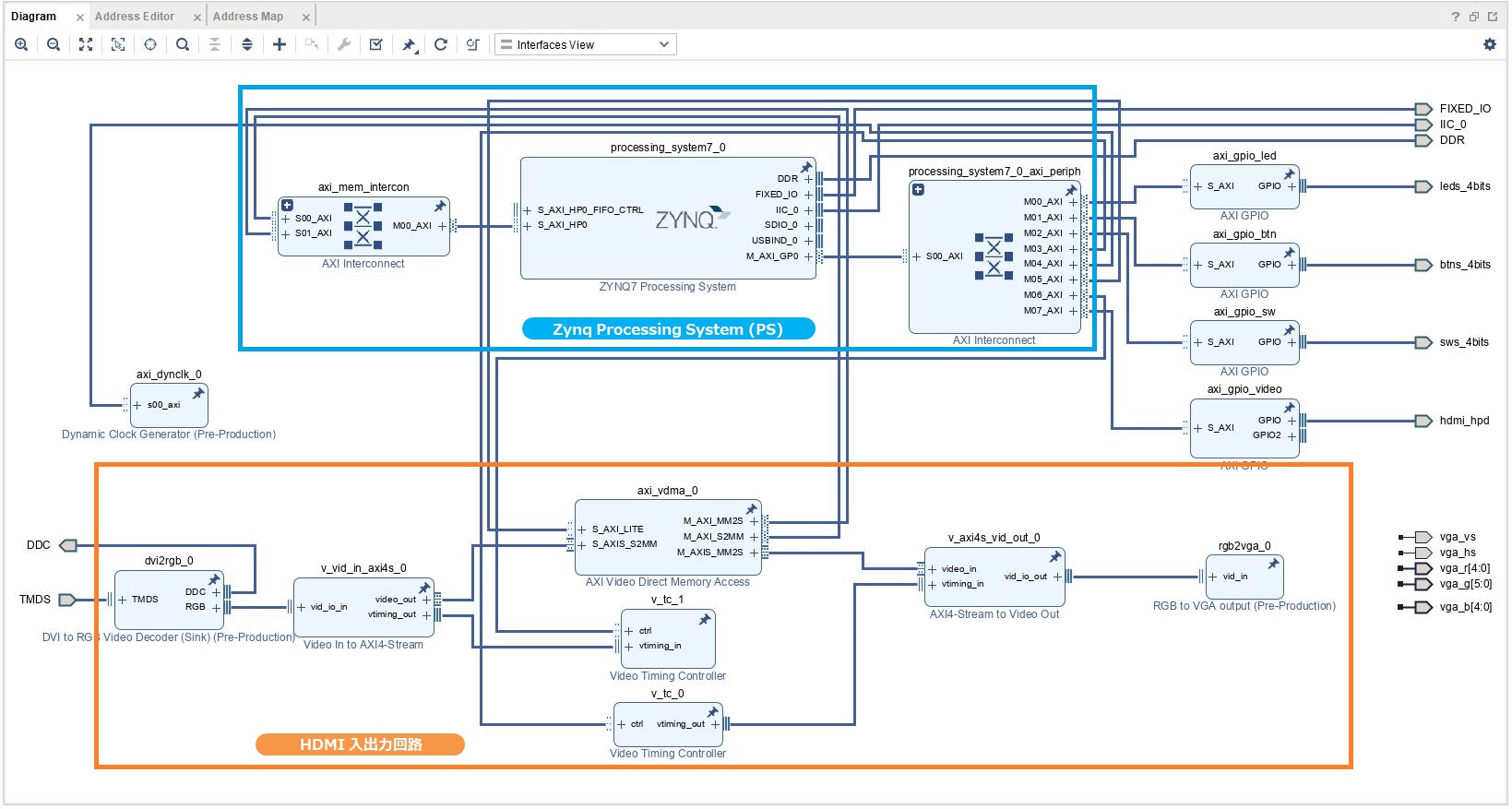

ブロックデザインの構成の説明

では、デモサンプルの読み込みによって作成されたブロックダイアグラムが、動作原理で説明したような構成になっているかどうかを確認しましょう。

少し構成が複雑ですので、[Interfaces View]に切り替えて、IPの構成がわかりやすくなるようにしましょう。

※[Interfaces View]への切り替えには、ブロックダイアグラムの右上の[Default View]をクリックし、[Interfaces View]に変更してください。

古いバージョンのVivadoでは確か実装されていなかったと思いますのでご注意ください。

[Interfaces View]への切り替えと合わせて、見やすくなるようにIPを並べました。

HDMI入出力回路の構成は、2章の動作原理で説明した通りの構成になっていることがわかると思います。

AXI VDMAとZynq PS部との送受信には、HPポートが使われていますね。

HPポートのインターコネクトのために、AXIインターコネクトが追加されています。

また、制御信号・ステータス信号を各IPとやり取りするためのバスにはGPポートが用いられ、こちらもAXIインターコネクトが追加されています。

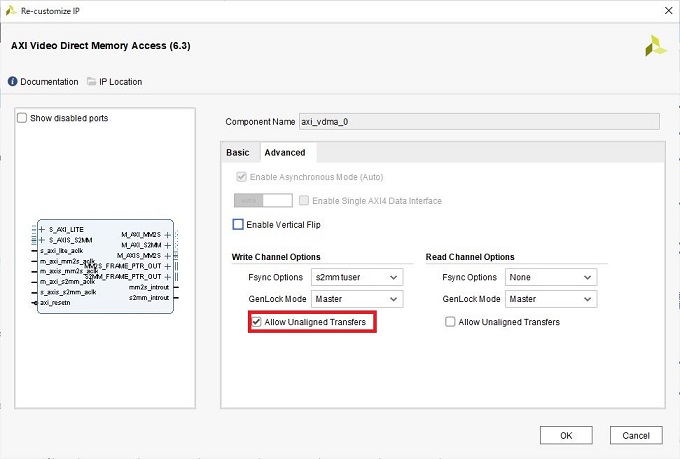

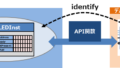

注:AXI VDMAの設定変更

動画像を出力するに当たり、AXI VDMAの設定を変更する必要がありましたので、記載しておきます。

DMA方式でDDRメモリに映像信号を書き込む際に、DRE(Data Realignment Engine)と呼ばれる機能を働かせる必要がありました。

読み込んだ設定では反映されていないようでしたので、以下の図のように[Allow Unaligned Transfers]にチェックを入れて、DREをイネーブルしておきましょう。

リファレンス・マニュアル(P.9)によると、

DREは「メモリへの整列されていないアクセスを可能とし、フレームバッファがメモリ内の任意のアドレスから開始できるようにする機能」とのこと。

映像信号がうまく整列していなくても、きれいに再整列してメモリに格納してくれる機能と私は解釈しています。

制約ファイルの作成

HDMIへの出力信号がFPGAのどのピンから出力されるか、制約ファイル上で定義します。

デモサンプルファイル内にはすでに制約ファイル[ZYBO_Master.xdc]が含まれています。(格納先は[src]>>[constraints]です。)、Tclスクリプトを読み込んだときにVivadoのプロジェクト内に制約ファイルは読み込まれています。

一部、ブロックデザイン上の端子では大文字になっているにもかかわらず、制約ファイル上では小文字になっていますので、修正が必要になりました。

例えば、制約ファイル上ではHDMI_DDCなどが小文字になっているので、大文字にしていく作業が必要でしたのでご注意ください。

#IO_L16N_T2_35

set_property PACKAGE_PIN G18 [get_ports HDMI_DDC_sda_io]

set_property IOSTANDARD LVCMOS33 [get_ports HDMI_DDC_sda_io]論理合成、配置配線、bitstreamファイルの作成、XSAファイルの作成

それでは、ブロックデザインの読み込みと制約ファイルの修正が完了したので、論理合成からXSAファイルの作成までを一気に行っていきます。

前回の記事と重複する内容になりますので、改めて確認したい方は[+]マークから詳細をご確認ください。

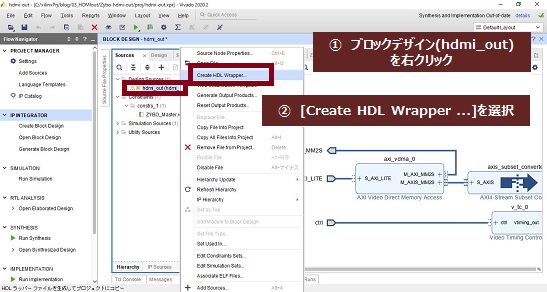

ブロックデザインからHDL記述への変換

読み込んだブロックデザインをもとにHDL(ハードウェア言語)を作成します。

ブロックデザインのデザイン名[hdmi_in]を右クリックし、[Create HDL Wrapper …]を選択します。

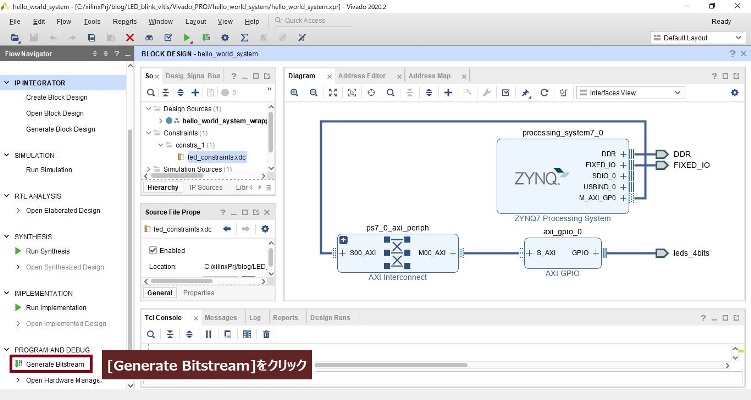

論理合成、配置配線、bitstreamファイルの作成

[Generate Bitstream]をクリックし、論理合成、配置配線、bitstreamファイルの作成までを行います。

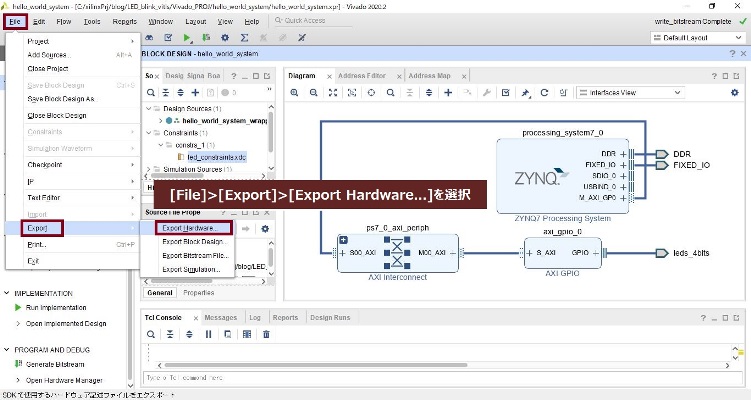

ハードウェアデザインのエクスポート(XSAファイルの作成)

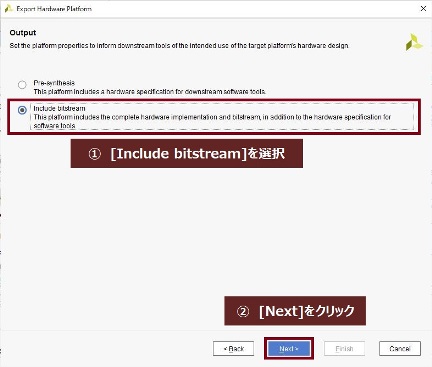

[File]から[Export]>[Export Hardware…]を選択

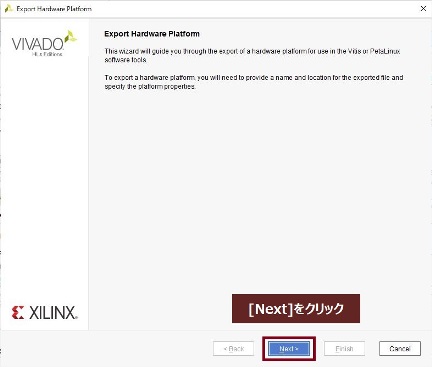

立ち上がった新しいウィンドウ上で、エクスポートの設定を確認していきます。

まず、[Next]をクリックします。

[Include bitstream]を選択し、[Next]をクリックします。

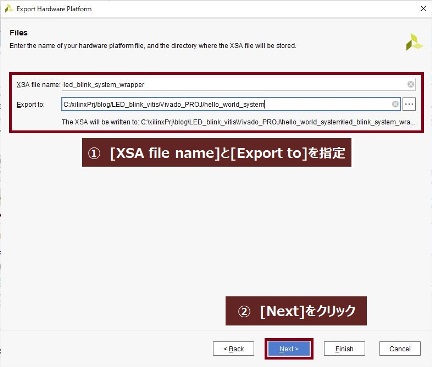

ファイル名とエクスポート先を指定し、[Next]をクリックします。

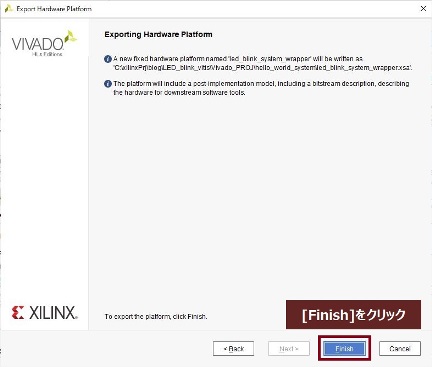

最後に、[Finish]をクリックして完了です。

お疲れさまです。

次回、ソフトウェア側のプログラムを読み込んでいきます。HDMI形式で入力した信号がVGA出力されるプログラムを解説していますので、ぜひご覧いただければと思います。

最後までご覧いただき、ありがとうございました。

次回の記事へのリンク

参考文献

Xilinx社のリファレンス・マニュアルを参考にしました。

https://www.xilinx.com/support/documentation/ip_documentation/axi_videoip/v1_0/ug934_axi_videoIP.pdf

https://japan.xilinx.com/support/documentation/ip_documentation/axi_vdma/v6_3/pg020_axi_vdma.pdf

コメント