AXI4

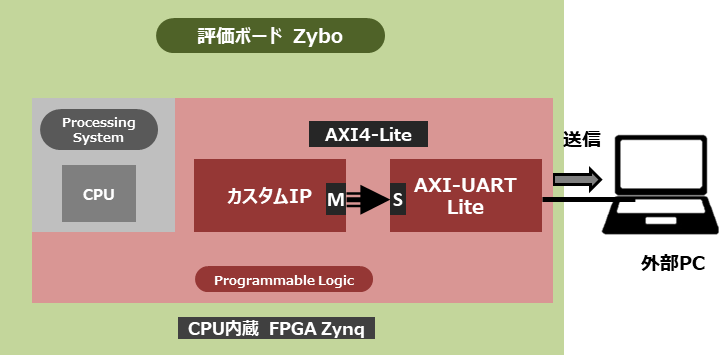

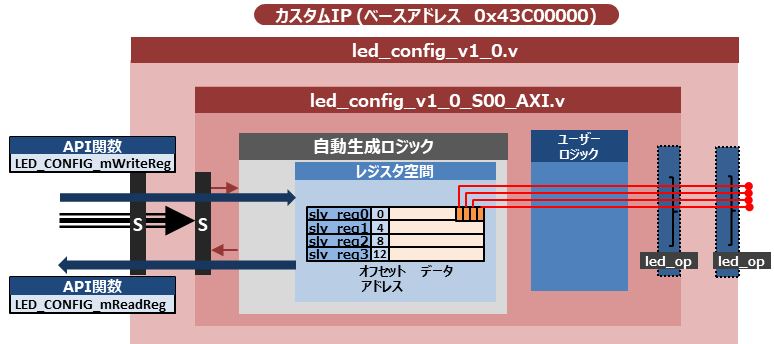

AXI4 自作RTLにAXI4-Liteインタフェース(M側)を追加する方法 (2) IPコアAXI-UART Liteのレジスタに書き込む方法

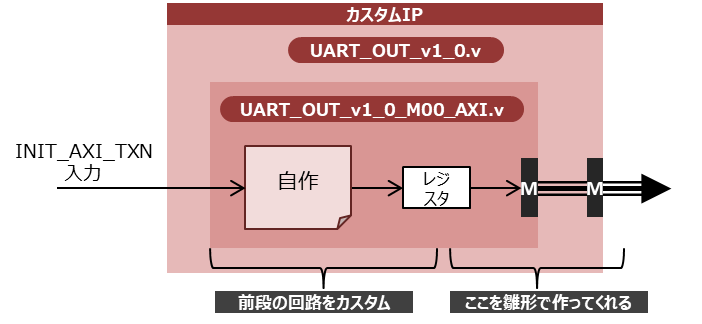

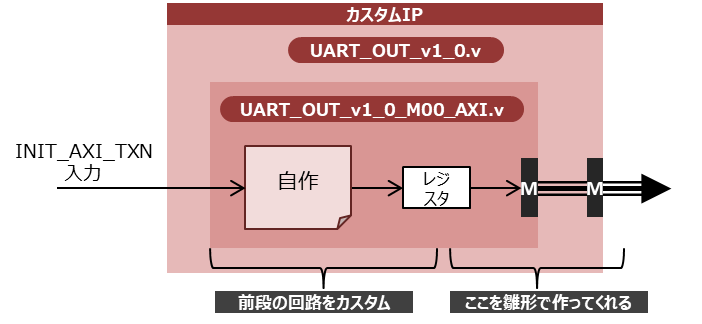

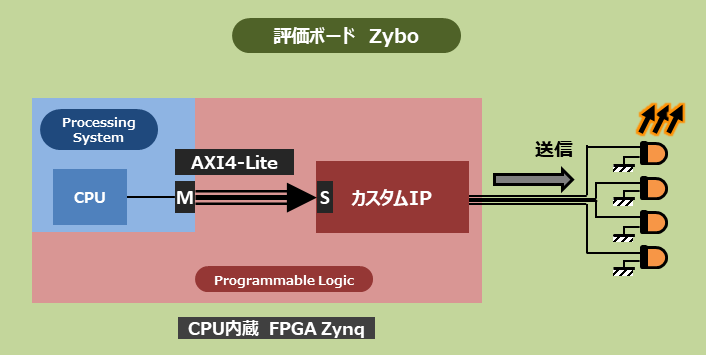

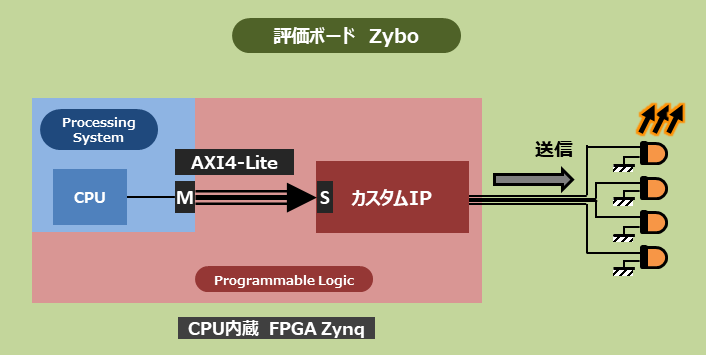

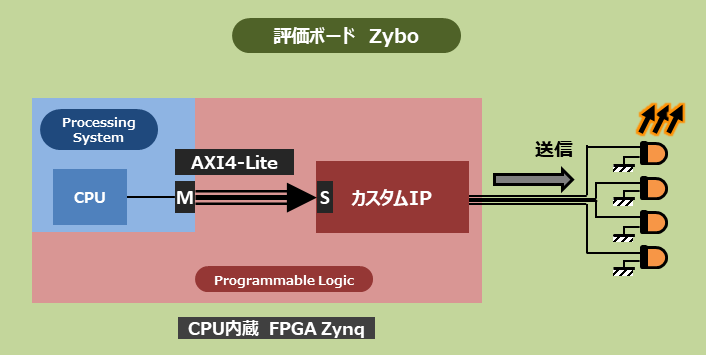

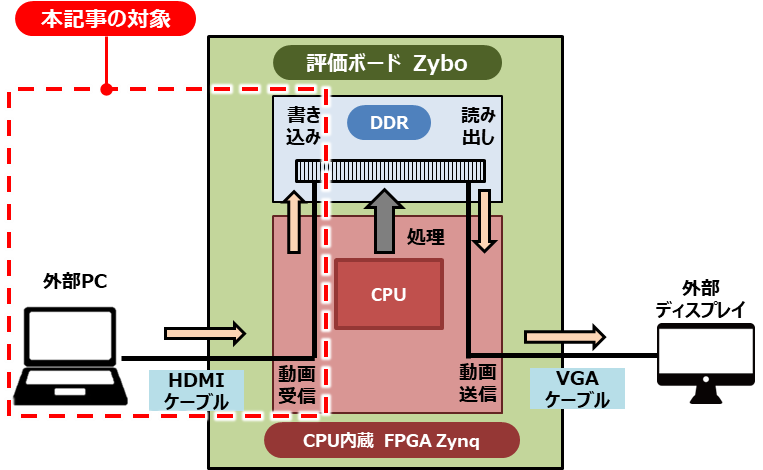

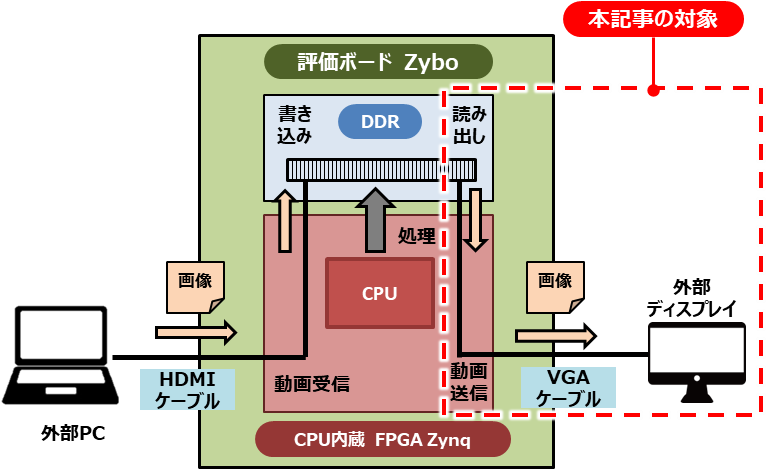

IPパッケージャーを使用してMaster側のAXI4-Liteインタフェースを追加する方法を解説しています。シリアル出力回路を例にXilinx社のIP”AXI UART Lite”のAXI4-Liteポートと接続可能なカスタムIPを作成しました。

AXI4

AXI4  AXI4

AXI4  AXI4

AXI4  Xilinx SoC

Xilinx SoC  AXI4

AXI4  AXI4

AXI4  Vitis

Vitis  Vitis

Vitis  Vitis

Vitis