Xilinx SoC

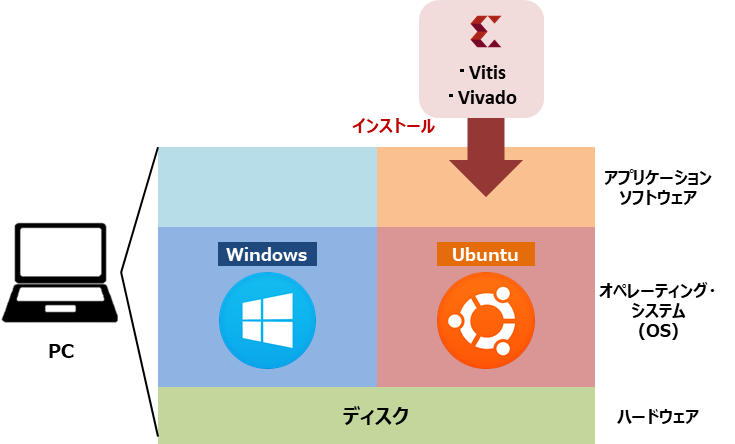

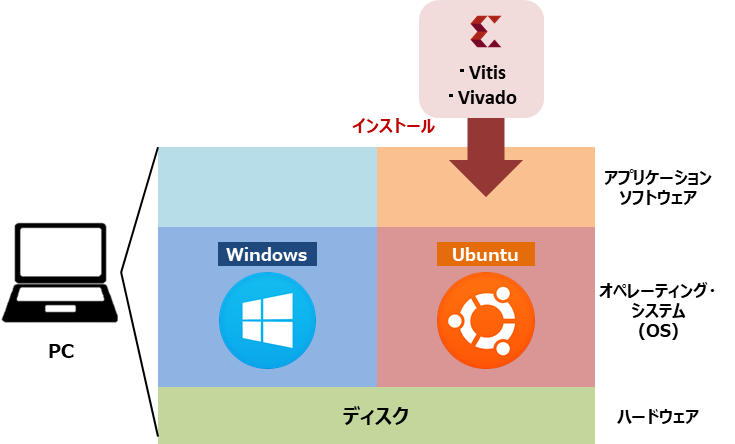

Xilinx SoC Ubuntu20.04にVitis IDE2021.1とVivado ML2021.1をインストール

UbuntuにXilinx社のVitis統合ソフトウェアプラットフォーム2021.1とVivado ML 2021.1をインストールしました。インストールにあたり、いくつか詰まったところもあったので、その解決方法を記事にまとめています。

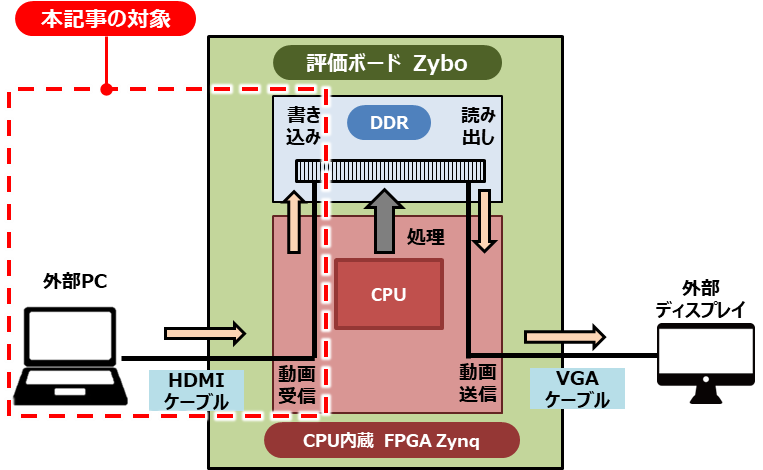

Xilinx SoC

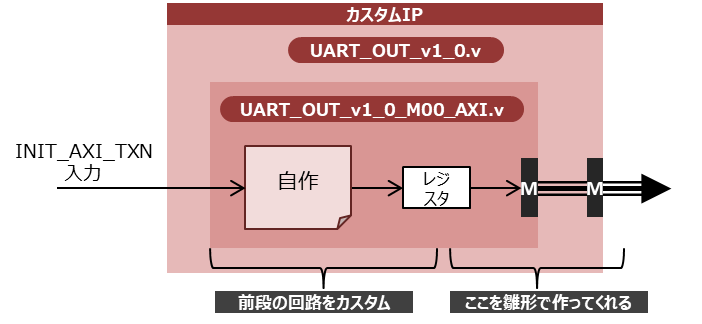

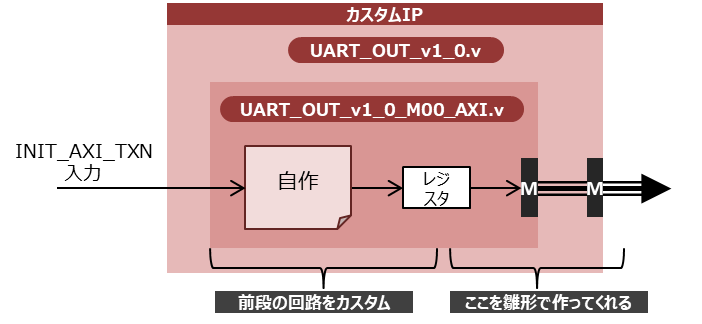

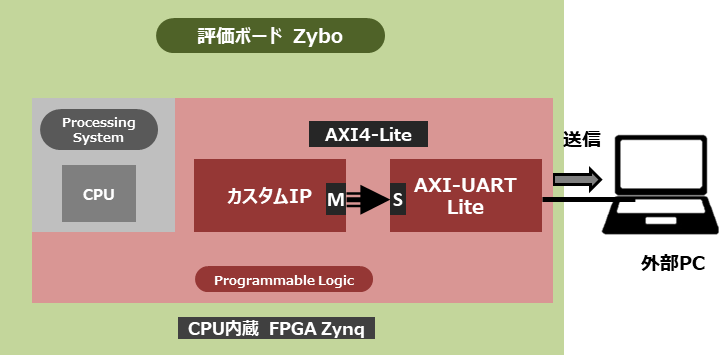

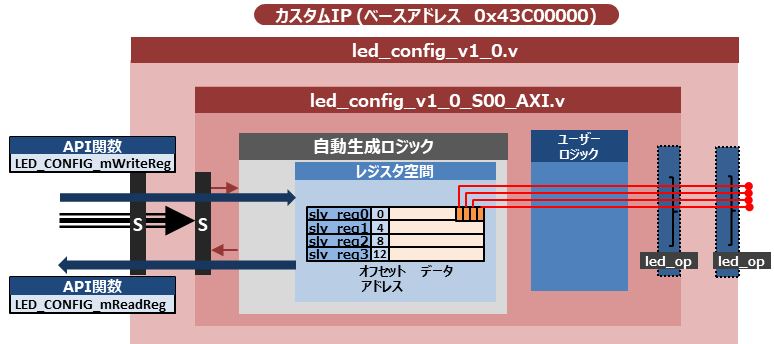

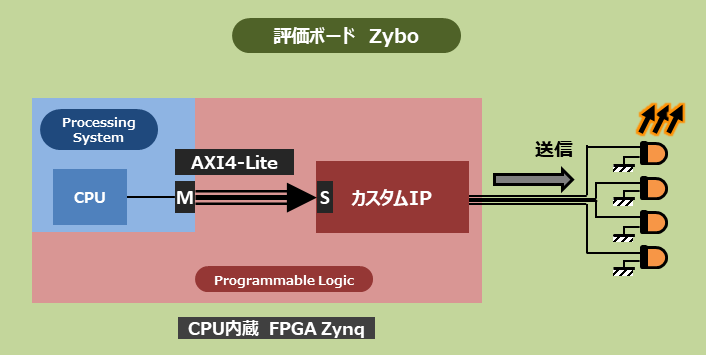

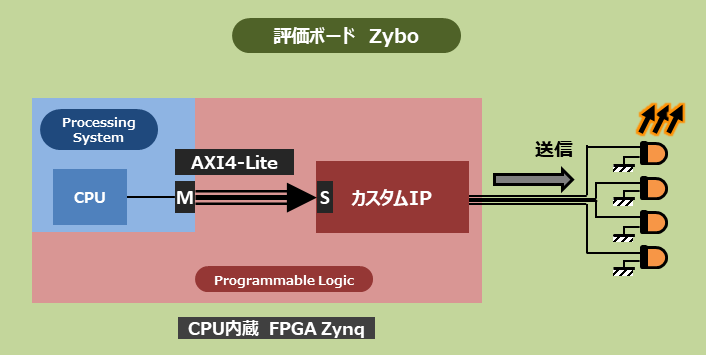

Xilinx SoC  AXI4

AXI4  AXI4

AXI4  AXI4

AXI4  AXI4

AXI4  Xilinx SoC

Xilinx SoC  AXI4

AXI4  AXI4

AXI4  Vitis

Vitis