Vitis

Vitis 【LED点滅編(4)】タイマー割り込みを行うAPIについて解説

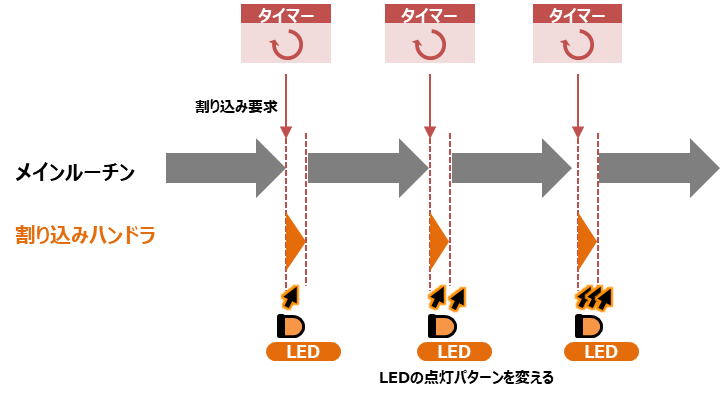

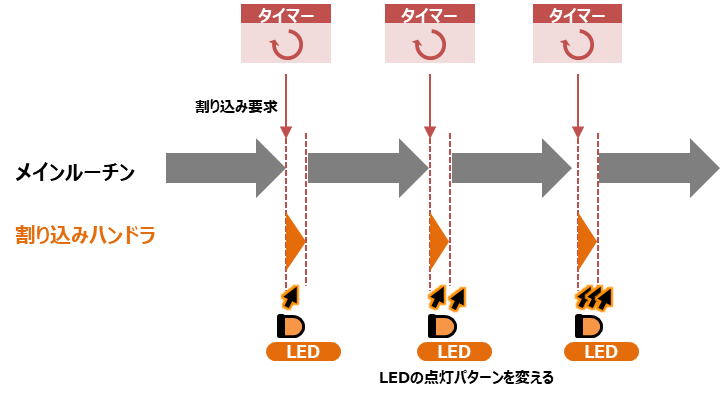

Zynqのプロセッサ上で割り込みをかける方法について解説します。AXI Timerからの割り込み要求に応じて割り込みがかかるLED点滅のアプリケーションを例にVitisやXilinx SDKでのAPIの使用方法についてまとめました。

Vitis

Vitis  Vitis

Vitis  Vitis

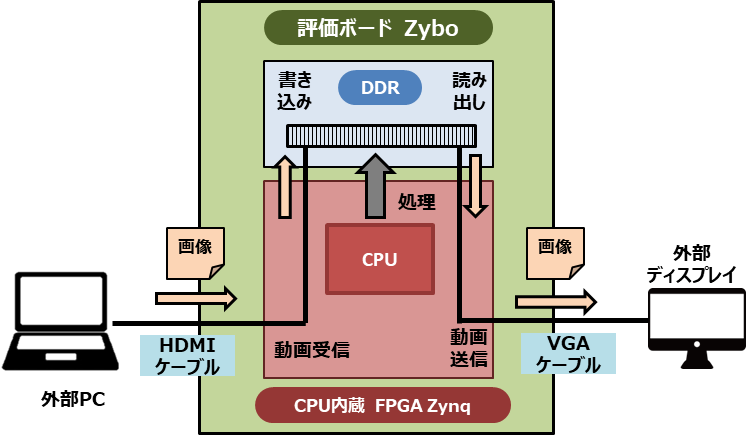

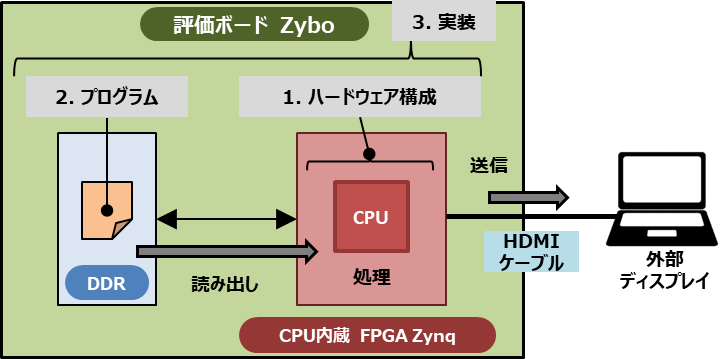

Vitis  Xilinx SoC

Xilinx SoC  Xilinx SoC

Xilinx SoC  Xilinx SoC

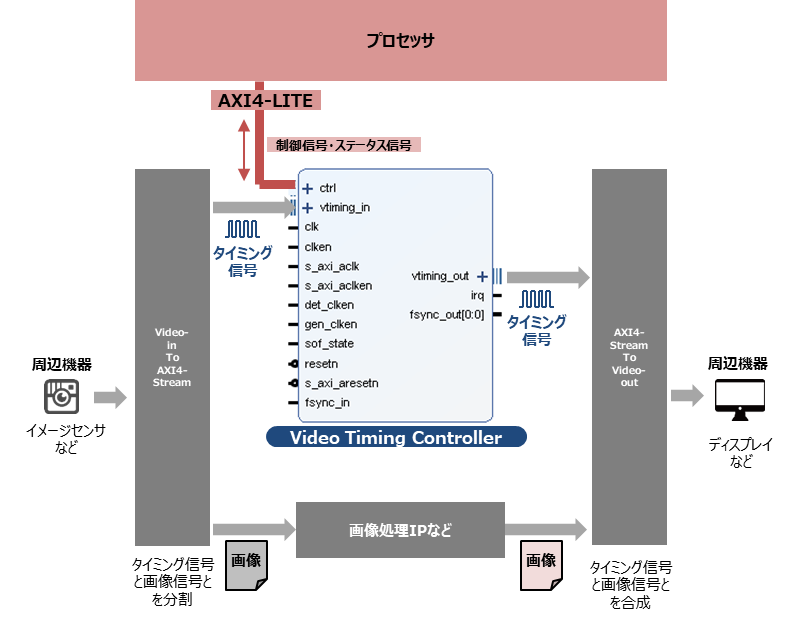

Xilinx SoC  IP

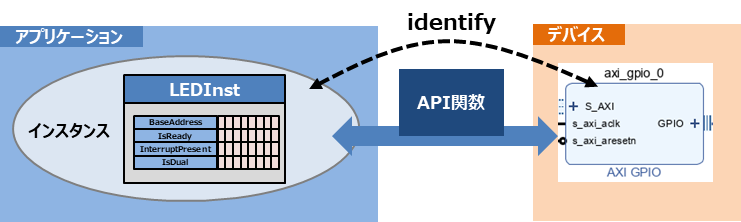

IP  Vitis

Vitis  IP

IP